# **FUTURE COMPUTING 2013**

The Fifth International Conference on Future Computational Technologies and Applications

ISBN: 978-1-61208-272-1

May 27- June 1, 2013

Valencia, Spain

# **FUTURE COMPUTING 2013 Editors**

Alexander Gegov, University of Portsmouth, UK

Petre Dini, Concordia University, Canada | China Space Agency Center, Beijing,

China

# **FUTURE COMPUTING 2013**

# **Foreword**

The Fifth International Conference on Future Computational Technologies and Applications (FUTURE COMPUTING 2013), held between May 27 and June 1, 2013 in Valencia, Spain, targeted advanced computational paradigms and their applications. The aim was to cover (i) the advanced research on computational techniques that apply the newest human-like decisions, and (ii) applications on various domains. The new development led to special computational facets on mechanism-oriented computing, large-scale computing and technology-oriented computing. They are largely expected to play an important role in cloud systems, on-demand services, autonomic systems, and pervasive applications and services.

We take here the opportunity to warmly thank all the members of the FUTURE COMPUTING 2013 Technical Program Committee, as well as the numerous reviewers. The creation of such a broad and high quality conference program would not have been possible without their involvement. We also kindly thank all the authors who dedicated much of their time and efforts to contribute to FUTURE COMPUTING 2013. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

Also, this event could not have been a reality without the support of many individuals, organizations, and sponsors. We are grateful to the members of the FUTURE COMPUTING 2013 organizing committee for their help in handling the logistics and for their work to make this professional meeting a success.

We hope that FUTURE COMPUTING 2013 was a successful international forum for the exchange of ideas and results between academia and industry and for the promotion of progress in the field future computational technologies and applications.

We are convinced that the participants found the event useful and communications very open. We hope that Valencia, Spain provided a pleasant environment during the conference and everyone saved some time to explore this historic city.

**FUTURE COMPUTING 2013 Chairs:**

**FUTURE COMPUTING General Chair**

Javier Aguiar, University of Valladolid, Spain

# **FUTURE COMPUTING Advisory Chairs**

Cristina Seceleanu, Mälardalen University, Sweden Hiroyuki Sato, The University of Tokyo, Japan Miriam A. M. Capretz, The University of Western Ontario - London, Canada Kendall E. Nygard, North Dakota State University - Fargo, USA Vladimir Stantchev, Berlin Institute of Technology, Germany Marek J. Druzdzel, University of Pittsburgh, USA

# **FUTURE COMPUTING 2013 Industry/Research**

Francesc Guim, Intel Corporation, Spain Wolfgang Gentzsch, Expert HPC, Germany

# **FUTURE COMPUTING 2013**

# **Committee**

## **FUTURE COMPUTING General Chair**

Javier Aguiar, University of Valladolid, Spain

# **FUTURE COMPUTING Advisory Chairs**

Cristina Seceleanu, Mälardalen University, Sweden Hiroyuki Sato, The University of Tokyo, Japan Miriam A. M. Capretz, The University of Western Ontario - London, Canada Kendall E. Nygard, North Dakota State University - Fargo, USA Vladimir Stantchev, Berlin Institute of Technology, Germany Marek J. Druzdzel, University of Pittsburgh, USA

# **FUTURE COMPUTING 2013 Industry/Research**

Francesc Guim, Intel Corporation, Spain Wolfgang Gentzsch, Expert HPC, Germany

# **FUTURE COMPUTING 2013 Technical Program Committee**

Ofer Arieli, The Academic College of Tel-Aviv, Israel

Mohsen Askari, University of Technology Sydney, Australia

Jan Blech, fortiss GmbH, Germany

Radu Calinescu, Aston University-Birmingham, UK

Alberto Cano, University of Córdoba, Spain

Miriam A. M. Capretz, The University of Western Ontario - London, Canada

Massimiliano Caramia, University of Rome "Tor Vergata", Italy

Chin-Chen Chang, Feng Chia University, Taiwan, R.O.C.

Sung-Bae Cho, Yonsei University, Korea

Rosanna Costaguta, Universidad Nacional de Santiago del Estero, Argentina

Zhihua Cui, Taiyuan University of Science and Technology - Shanxi, China

Marc Daumas, INS2I & INSIS (CNRS), France

Isabel Maria de Sousa de Jesus, ISEP-Institute of Engineering of Porto, Portugal

Leandro Dias da Silva, Federal University of Alagoas, Brazil

Marek J. Druzdzel, University of Pittsburgh, USA

Dietmar Fey, Friedrich-Alexander-University Erlangen-Nuremberg, Germany

Francesco Fontanella, Università degli Studi di Cassino e del Lazio Meridionale, Italy

Miguelo Garcia, Polytechnic University of Valencia, Spain

Wolfgang Gentzsch, Consultant, Germany

Victor Govindaswamy, Texas A&M University-Texarkana, USA

Michael Grottke, University of Erlangen-Nuremberg. Germany

Miguel Angel Guevara López, Universidade do Porto, Portugal

Francesc Guim, Intel Corporation, USA

Yongjian Hu, University of Warwick - Coventry, UK

Jong-Gyu Hwang, Korea Railroad Research Institute (KRRI), Korea

Muhammad Iftikhar, Universiti Malaysia Sabah (UMS), Malaysia

Dalia Kriksciuniene, Vilnius University, Lithuania

Carlos León de Mora, Universidad de Sevilla, Spain

Lu Liu, University of Derby, UK

Yu-lung Lo, Chaoyang University of Technology, Taiwan

José María Luna, University of Córdoba, Spain

Constandinos Mavromoustakis, University of Nicosia, Cyprus

Ehsan Mousavi, University of Science and Technology - Tehran, Iran

Susana Munoz Hernández, Universidad Politécnica de Madrid, Spain

Kazumi Nakamatsu, University of Hyogo, Japan

Isabel L. Nunes, Universidade Nova de Lisboa - Caparica, Portugal

Panos M. Pardalos, University of Florida, USA

Przemyslaw Pochec, University of New Brunswick, Canada

Alex Popa, Aalto University, Finland

Aurora Pozo, Federal University of Paraná, Brazil

Prakash Ranganathan, University of North Dakota-Grand Forks, USA

Ivan Rodero, NSF Center for Autonomic Computing / Rutgers the State University of New Jersey, USA

Aitor Rodriguez, University Autonoma of Barcelona, Spain

Hiroyuki Sato, The University of Tokyo, Japan

Cristina Seceleanu, Mdh, Sweden

Georgios Sirakoulis, Democritus University of Thrace - Xanthi, Greece

Devan Sohier, Université de Versailles - St-Quentin-en-Yveline, France

Young-Joo Suh, Pohang University of Science and Technology (POSTECH), Korea

Antonio J. Tallón-Ballesteros, University of Seville, Spain

Steffen Thiel, Furtwangen University of Applied Sciences, Germany

Michael N. Vrahatis, University of Patras, Greece

Alexander Wijesinha, Towson University, USA

Zhengping Wu, University of Bridgeport, USA

Chao-Tung Yang, Tunghai University, Taiwan R.O.C.

Hongji Yang, De Montfort University (DMU) - Leicester, UK

Peng-Yeng Yin, National Chi Nan University, Taiwan

Zhibin Yu, Shenzhen Institutes of Advanced Technology, Chinese Academy of Sciences, China

Yong-Ping Zhang, Huawei Technologies Co., Ltd., China

Zhiyong Zhang, Henan University of Science and Technology, P.R. of China

# **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

# **Table of Contents**

| Eliminating the Operating System via the Bare Machine Computing Paradigm  Uzo Okafor, Ramesh Karne, Alexander Wijesinha, and Patrick Appiah-kubi                                                                                                 | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| An Orbit Tracking Algorithm in Quantum Systems Shuang Cong and Jianxiu Liu                                                                                                                                                                       | 7  |

| Face Recognition Using 1DLBP Texture Analysis  Amir Benzaoui and Abdelhani Boukrouche                                                                                                                                                            | 14 |

| Enhancing Hebbian Learning in Biological Neural Cultures Through Electrical Stimulation Victor Lorente, Jose Manuel Ferrandez, Eduardo Fernandez, and Felix de la Paz                                                                            | 20 |

| Power Consumption-based Application Classification and Malware Detection on Android Using Machine-<br>Learning Techniques  Thomas Zefferer, Peter Teufl, David Derler, Klaus Potzmader, Alexander Oprisnik, Hubert Gasparitz, and Andrea Hoeller | 26 |

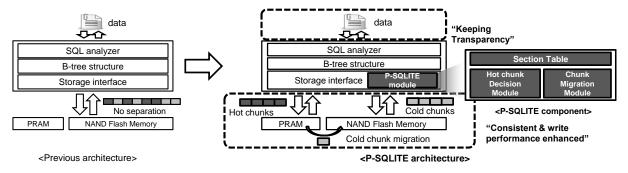

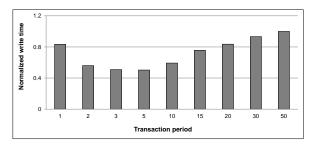

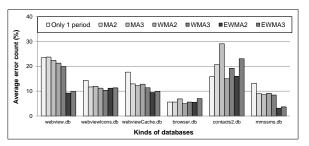

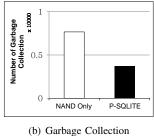

| P-SQLITE: PRAM-Based Mobile DBMS for Write Performance Enhancement Woong Choi, Sung Kyu Park, Seong Min Kim, Min Kyu Maeng, Ki-Woong Park, and Kyu Ho Park                                                                                       | 32 |

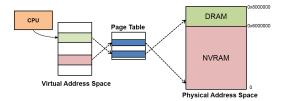

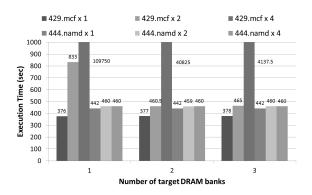

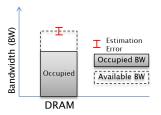

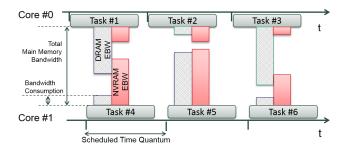

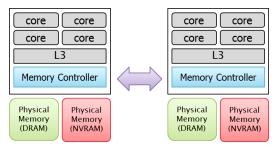

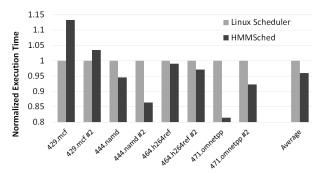

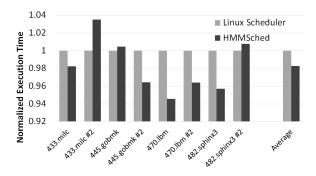

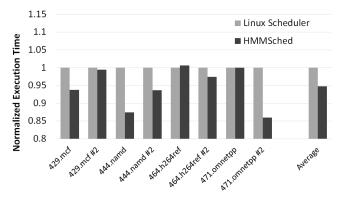

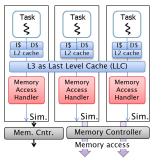

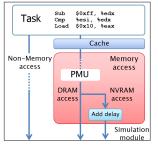

| HMMSched: Hybrid Main Memory-Aware Task Scheduling on Multicore Systems Woomin Hwang and Kyu Ho Park                                                                                                                                             | 39 |

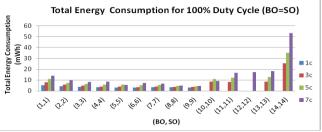

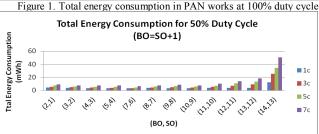

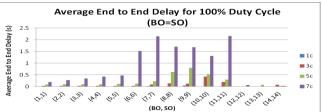

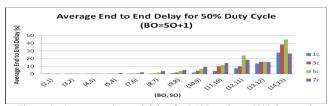

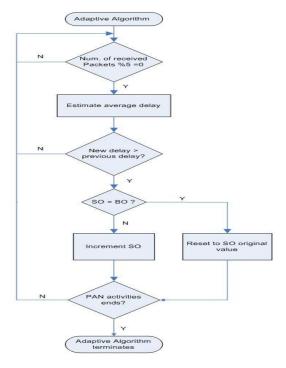

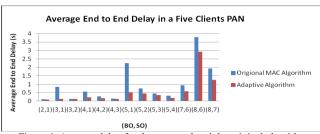

| Optimal Beacon and Superframe Orders in WSNs  Marwa Salayma, Wail Mardini, Yaser Khamayseh, and Muneer Bani Yasin                                                                                                                                | 49 |

| Twitter Data Preprocessing for Spam Detection  Myungsook Klassen                                                                                                                                                                                 | 56 |

| Exploring HADOOP as a Platform for Distributed Association Rule Mining Shravanth Oruganti, Qin Ding, and Nasseh Tabrizi                                                                                                                          | 62 |

| An Alternative Archiving Technique for Evolutionary Polygonal Approximation  Jose Luis Guerrero, Antonio Berlanga, and Jose Manuel Molina                                                                                                        | 68 |

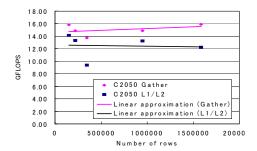

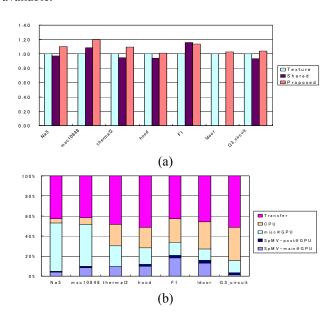

| Future Irregular Computing with Memory Accelerators  Noboru Tanabe, Junko Kogou, Sonoko Tomimori, Masami Takata, and Kazuki Joe                                                                                                                  | 74 |

# Eliminating the Operating System via the Bare Machine Computing Paradigm

Uzo Okafor, Ramesh K. Karne, Alexander L. Wijesinha, and Patrick Appiah-Kubi Department of Computer and Information Sciences Towson University Towson, MD 21252 USA

uokafo1@students.towson.edu, {rkarne, awijesinha, appiahkubi}@towson.edu

Abstract - Computer applications typically run under the control of intermediary system software that is in the form of an operating system such as Windows or Linux, or a small kernel. The application could also be embedded within the operating system or kernel itself. This paradigm makes applications dependent on an intermediary software layer. An alternative approach is to eliminate this layer by writing computer applications that can run directly on the hardware. This approach takes a small or tiny kernel to its extreme, eliminating the operating system, which results in a novel bare machine computing paradigm. In this paper, we describe the bare machine paradigm, and illustrate how to build selfsupporting bare machine applications by eliminating application dependence on an operating system or kernel. The new paradigm requires that the developer be aware of the underlying hardware resources and use them efficiently for the needs of a given application suite. We also describe a set of generic bare interfaces that can be used across many pervasive devices as well as ordinary desktops and laptops. These interfaces have made it possible to build large bare applications. The bare machine paradigm paves the way for software interfaces to be incorporated into a chip, introducing a computing model where applications are independent of any intermediary software.

Keywords - bare machine applications; bare machine computing; middleware; direct hardware interfaces; operating systems.

# I. INTRODUCTION

Building bare machine applications, which are independent of any intermediary software, is daunting due to constraints imposed by the existing computer architecture and development environments. Most CPUs are designed to work with an operating system (OS) or kernel and do not provide any interfaces to directly control the hardware. In some cases, the kernel or virtual machine may allow an application direct hardware access, but does not fully relinquish its control to the application. However, for certain specialized applications and secure systems, even the presence of a small kernel may prevent the application from fully controlling its environment and managing the hardware.

We propose to eliminate the OS (or kernel) and give full control to applications. These applications are then able to run on the bare hardware without the need for any additional software layers. There is no persistent storage or any other resource to secure on a bare machine, device, or computing system. Moreover, only one bare application suite runs at a time. When an application is not running, the machine is not running any other code. It simply has memory, processors and an I/O controller to communicate with the applications when needed. Instead of an OS or kernel providing resources, an application suite manages the hardware. This does not mean that the applications replicate OS functionality. Rather, applications only contain code that is required for a given application suite. An application suite is modeled as an Application Object (AO) [6] that carries its own application and execution environment. For example, an AO may consist of a text processor/editor, a Webmail client, and a Web browser, and bare interfaces to the hardware. An AO programmer needs to have knowledge of the underlying resources, since an AO controls and manages all the hardware when it runs. A bare machine user carries a removable mass storage device to boot, load and run the application suite, thus making the machine bare when the AO is not loaded (since no OS or kernel is needed to run the suite).

When such bare machines are built, they become ownerless and can be used by anyone, anytime, and anywhere. Many complex bare applications have been built to illustrate the bare machine computing (BMC) paradigm. These include a Web server [4], Webmail server [1], conventional (non-HTTP) email server and client, VoIP soft-phone [9], SIP server, and bare PC clusters using split servers [13]. The development of such applications served as the motivation for designing the direct hardware interfaces to a bare PC (x86 architecture). These interfaces are generic and can be used to construct any bare machine application. One can make these interfaces and the BIOS part of the hardware in the future, thus creating a pure BMC environment, where there is no other software needed to run computer applications. A high-level methodology for developing bare machine applications was outlined previously [10]. Here, we provide details of how to develop such bare machine applications by using a set of generic hardware interfaces. In particular, this paper describes the direct hardware interfaces needed to eliminate the intermediary OS.

The rest of the paper is organized as follows. Section II provides the motivation for this work. Section III describes the bare machine computing paradigm and its characteristics. Section IV illustrates the development of bare machine applications using a step-by-step process. Section V presents the direct generic hardware interfaces. Sections VI, VII and VIII respectively cover the use of a bootable USB, memory map, and the novel features of this approach. Finally, Section IX gives the conclusion.

### II. MOTIVATION

The following considerations serve as the motivation for developing BMC applications based on the underlying paradigm: the proliferation of operating systems (OS) and frequent new releases to replace them; the rapid obsolescence of existing computer applications; the myriad of programming languages and interfaces; and the heterogeneity of computer architectures and platforms. While many arguments can be given to support the current evolution of conventional systems/platforms and their advantages, the BMC paradigm has been shown to be feasible for building a variety of complex applications such as the servers, clients, and high-performance systems noted above

Most current systems use complex concurrency control mechanisms, paging, virtual memory, and other well-known concepts that have evolved due to lack of large memory, memory costs, shared resources, and the need to serve multiple users. Under those conditions, computing evolved towards complex systems with rapid obsolescence and less security. The BMC paradigm [7] enables applications to directly communicate with hardware, thus eliminating all middleware. Using this paradigm, applications can be written in C/C++ or other languages, where an AO programmer can directly call hardware interfaces, as originally proposed in [8]. This paper extends those ideas to address general purpose development of bare machine computing applications and a set of generic interfaces to the hardware.

# III. BARE MACHINE COMPUTING PARADIGM

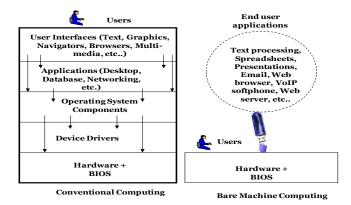

The BMC paradigm was originally referred to as dispersed operating system computing (DOSC) [7], but we have seen further evolution of DOSC into the BMC concepts as shown in Fig 1. A conventional OS, kernel or embedded software acts as middleware between the hardware and an application. An application programmer is isolated from an application's execution environment, resource control and management.

Figure 1. Conventional OS versus BMC paradigms

That is, the programmer has no direct control of the program's execution or the resources needed. In the BMC

paradigm as shown in Fig 1, the OS is eliminated and the AO programmer is totally responsible for managing hardware resources. The AO programmer has knowledge and full control over a given application as well as its execution. Each AO only carries its needed controls and the direct hardware interfaces. The AO programmer is a domain expert for a given set of applications that are contained in a given AO. The BMC paradigm differs from conventional computing in two major ways. First, the machine is bare with no existing software and protected resources. Second, an AO programmer controls the program's execution and manages the hardware.

The BMC paradigm makes a computing device ownerless and simplifies the design of secure systems since there are less avenues of attack and no underlying middleware that an attacker can control. Viewed another way, when a device is bare and contains no valuable resources such as a hard disk or kernel, there is nothing to own or protect. In BMC, mass storage is external and detachable. The mass storage can also be on a network. In this approach, an AO is built for a given set of applications to run at a time on a machine as a single monolithic executable. The boot, load, executable, data and files are stored on a mass storage device such as a USB. When a USB is plugged into a computer, the machine boots and runs its own program without using any extra software or external programs. This implies that no dynamic link libraries (DLLs) or virtual machine code are allowed in this approach. What runs in the machine, is exactly what has been loaded (and nothing else).

This computing paradigm is different from conventional computing approaches since it is based on applications instead of computing environments. This is not a mini-OS or kernel, as there is no centralized program running in the machine to manage resources. Instead, the resources are managed by the applications themselves and run without using any OS/kernel or intermediary software.

A variety of attempts have been made to eliminate OS abstractions or bypass the OS. However, none eliminate the kernel or OS altogether. Thus, while the BMC paradigm resembles approaches that reduce OS overhead and/or use lean kernels such as Exokernel [2], IO-Lite [12], Palacio [11], and the Hardware Abstraction Layer [14] in Java, there are significant differences. These include self controlled applications and programmer-driven execution, and the lack of centralized code that manages system resources. A model to analyze tradeoffs between feature-rich and minimalist or "barebone" systems is presented in [15]. While such minimalist systems usually require an operating system or kernel, they may have also some characteristics in common with BMC systems.

# IV. BMC APPLICATION DEVELOPMENT

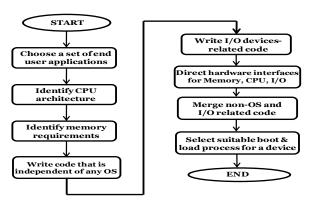

In BMC, a suite of applications such as a text processor, Webmail server and Web browser can be bundled together and run without any OS or kernel support. Fig. 2 illustrates the major steps involved in developing

BMC applications. First, a choice has to be made about the suite of applications; next, the architecture of the CPU on which they will run has to be identified. Using today's CPUs, constructing a BMC application is a daunting task as they provide neither direct hardware interfaces, nor a development environment that facilitates applications independent of an OS. For example, a bare PC requires the BIOS to boot, and an ARM processor requires a UBOOT tool. The program counter of a given processor is not directly accessible to the programmer. In a machine with an x86 CPU, the program counter can only be loaded by jumping to the task segment, where its value is stored and updated by the CPU. In a bare machine application, the program counter must be handled inside an application and not controlled by an OS or other software.

Memory needs or requirements must be considered for a given application's code, data and stack. The application programmer has to determine memory areas for the code, data and stack, as these applications run in a real memory. Real memory is cheap and affordable today. It is therefore feasible to avoid paging and virtual memory overhead, and the associated management. The absence of any other software in the system eliminates many unnecessary features commonly found in today's technology. Most BMC application suites only require small amounts of memory compared to OS-based applications. For very large applications, one can use mass storage to provide extended storage using swapping techniques. Section 7 describes details of the memory map created for some real-world applications using the BMC paradigm.

The next step is to construct an application suite using programs that are independent of any OS. This application suite should be able to run on any compatible CPU without changes or adaptations. Different CPU architectures have different compilers to compile code. This requires that I/O related code be identified and direct hardware interfaces be deployed. One of the key elements in writing BMC code is being able to differentiate between code that is OS dependent, code that is OS independent and code that is I/O related. For example, file I/O is OS dependent code and a for-loop is OS independent code. User interfaces to support keyboard, mouse and display are all I/O related code.

Figure 2. Steps in developing bare machine applications

Once OS dependent code and I/O related code are written (as hardware interfaces), they can all be integrated with the rest of the OS independent code and run as a single monolithic executable. The above approach introduces many challenges that must be addressed when developing BMC applications. They include the boot-up process and loading of an application suite. Each computing device is different in its boot process and the internal details are often hidden. Similarly, loading an application on a bare device also poses difficulties as it requires readily available tools that are OS dependent. Developing an OS independent loader requires a thorough knowledge of the CPU architecture and its development environment. Domain knowledge and related expertise for each CPU device are required to develop the bare boot and load processes.

# V. DIRECT HARDWARE INTERFACES

Conventional computer applications and programming languages use OS calls or system calls injected at link time from an OS such as Windows [16] or Linux [3]. These calls include memory, keyboard, terminal screen, network, mass storage, and interrupts. Some OSs include in their repertoire other commonly used OS-independent functions such as memory copy, string operations and concurrency control that require system calls. Computer applications and the programmer expect these calls or interfaces to be included at compile and link time by a given compiler and linker.

Bare machine applications require system call equivalents (direct hardware interfaces) that are independent of any OS or kernel. These interfaces are directly controlled and accessed by an AO programmer. All of the above are factors to consider in determining the number of direct hardware interfaces needed for a suite of BMC applications. Some direct hardware interfaces used in BMC applications are discussed below.

# A. Static and Dynamic Memory

Static memory needs depend on the size of code, data and stack needed to run a program. When an executable is created, this information is available to the programmer. Thus, for a given executable, one can specify its requirements for memory. An AO can also be designed that can read the existing memory and restructure its code, data and stack in real memory and external mass storage or network. The code image is small as there is only one AO running at a time in the machine, and applications that are related are grouped to run together.

Dynamic memory needs are however not known until run time. In a bare machine application, an AO programmer estimates the dynamic memory. Appropriate exceptions for memory can be set to manage dynamic memory; when large dynamic memory needs arise, one can use secondary storage in place of large dynamic memory. System calls similar to malloc() and free() can be designed to support dynamic memory management. One can allow the memory

controller to communicate with an AO and thus provide appropriate memory interfaces to manage memory in the AO. As memory technology improves and becomes cheaper, it is also conceivable to assume full address space (4GB in a 32-bit architecture) in a machine to avoid all memory management issues and provide direct control to a given AO.

# B. User Interfaces

The most common user interfaces are keyboard, mouse, touch-screen and terminal screen. These resources are managed by the OS in conventional systems. In bare machine applications, keyboard interfaces are part of an AO where the keyboard interrupt code places the data in a user buffer. Similarly, mouse data is also placed in a user buffer. An AO programmer designs the code to directly interface with a keyboard or a mouse. The terminal screen is usually controlled by a video memory or its graphics adaptor. An AO programmer can directly store output in video memory or write a bare video driver to control the screen. All device drivers supporting a bare application have to be bare and provide direct hardware interfaces to applications. They cannot, as is done, when an OS is present, be hidden from the application programmer. Other user interfaces have to be handled in a similar manner to the above interfaces.

# C. Network Interfaces

Most ordinary computing devices today have one wired and one wireless network interface. The device drivers for a network interface are controlled by underlying OS. Bare machine device drivers that provide direct network interfaces to an AO are needed in BMC. Instead of current OS-dependent network drivers, an AO programmer can initialize a network driver, configure relevant internal registers, and read or write to buffers and control registers. Such a design allows direct communication to applications and avoids the need for any middleware. As the drivers are now encapsulated within an AO, the network hardware is not accessible to other applications when a given application suite is running in the machine. A bare PC USB device driver and its implementation are described in [5].

# D. Process Interfaces

Many computer applications require process creation, deletion and management, which are usually controlled by an OS. In Intel x86 processors, process control and state are maintained by the CPU in a task segment. Interrupt gates are used to switch from one task to another. That can be done in a bare environment since these interfaces are accessible to an AO programmer. Control of the CPU is placed in an application program for creation of a new process (or a task). The global descriptor table (GDT) and local descriptor table (LDT) entries are used by the AO programmer to control task memory. Thus, when a machine becomes bare, the CPU and tasks are managed by an AO

programmer. Task management in a bare machine is much simpler than in a conventional system, and the code size is also smaller compared to an OS-supported system. A conventional Web server system may be complex and create over 7000 tasks (in an x86 box) to provide high performance [4]. Process interfaces can eventually be generalized and made available to an AO programmer for any given CPU architecture. Today's machines hide all these interfaces under an OS or some form of similar middleware.

# E. File Interfaces

In conventional systems, a file system is part of the operating system. File systems use some standard specifications such as FAT32 or NTFS. Files can be transported across multiple operating systems and applications if they use standard specifications in their design. In bare machine applications, persistent data is under the control of an AO programmer and the data itself is part of an AO. Programmers can use their own file storage specification or use a standard specification to transport files to non-bare systems. One can also do a raw file system in an AO to avoid all file management complexities and hide the files within an AO (the only AO in which they are visible). This may be the most secure way to implement a file system. File transfers can also be accomplished through a network or by message passing. A given file system interface uses a bare device driver and controls the relevant device operations.

# F. Boot and Load Interfaces

Boot and load facilities are usually under control of the OS and the underlying BIOS calls. In BMC, these interfaces are controlled by the AO programmer to facilitate bare machine applications. Soft and hard boot can be used to control the machine when needed in bare machine applications. These interfaces also vary across platforms; ideally, a standard boot and load mechanism to run bare machine applications across multiple CPU architectures and machines is the best solution (what is described in Section VII, is a method that has been implemented for x86 Intel CPUs).

# G. Compile, Link and Library Issues

Compilers and linkers generate different formats for executables, which pose problems in loading and running bare machine applications. There is a need for homogenization in these tools to develop common bare machine applications that can run on many pervasive devices. New programming tools can be developed to compile bare machine applications using existing libraries and batch files, or new features can be added into existing Microsoft Visual Studio and Eclipse development tools to provide bare machine compilation options. Common libraries such as string operations, memory operations, locking, shared memory, message passing, and concurrency

control are system dependent and part of the OS libraries. However, they can be generalized and designed to run across many CPU architectures.

# VI. BOOTABLE USB

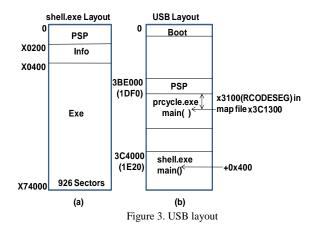

In the BMC paradigm, applications are carried on a removable storage medium such as a CD/DVD or a flash drive. This device also carries a boot program to boot and load its own application object suite. A typical way to create a bootable USB is as follows. A bootable USB is created using a special tool written in C and assembly language. This tool is a batch file that runs in a DOS window. The USB is formatted for FAT32 before its use. The bootable USB should have three files as shown in Fig. 3b. The boot file is stored in the boot sector (#0), the prcycle.exe file is stored at 0x3be000, and the application file (shown in Fig. 3a as shell.exe), is stored at 0x3c4000.

The prcycle.exe file (22, 037 bytes in size) contains assembly code to boot a bare PC, provides the user interface/menu, and facilitates the loading of AOs (in this instance, shell.exe). It enables the switching from real to protected mode and vice versa for handling low-level interfaces. It also contains, IDT, GDT, TSS and BIOS interrupts to provide the AO programmer with direct control of the CPU. This part of the application code thus plays a key role in enabling the programmer to manage the hardware resources in a bare PC. In summary, the batch file copies files onto the USB, installs a boot program, and creates a bootable USB. This entire process does not require any software other than what resides on the USB (and is thus part of the bare PC application). There is no dependence on any specialized commercial tool or software. This enables bare PC applications to be independent of any OS-related environments and tools. It is also possible to use existing boot tools to create a bootable USB; however those tools must guarantee high security if needed in a system. The approach proposed here demonstrates building bare machine computer applications in a single environment where every aspect of software development is controlled by an AO programmer with no other dependencies. This approach facilitates enhanced security to computer applications.

### VII. MEMORY MAP

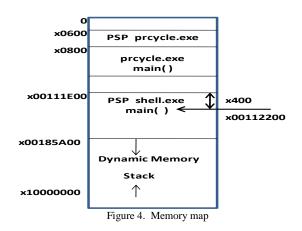

As discussed in section 4, the AO programmer needs to design the real memory layout when developing a bare PC application. Fig. 4 shows a typical memory layout for a given application suite. An AO programmer prepares this map before designing a given application suite. The prcycle.exe program is used on the bare platform to load the AO at 0x600 in real mode memory. The main() entry point for prcycle.exe is located at 0x3100, which can be obtained from the prcycle.map. When the PC is booted, it must jump to **0x3900** as instructed by this memory map. A user loads the example application (shell.exe) by using the menu provided by prcycle.exe (not shown here). The executable for this AO is loaded at 0x00111E00 as shown in Fig. 4. The reason for using this particular address for loading shell.exe is discussed below. Visual Studio 8.0 (and later editions) of compilers behave differently than the previous versions when generating an exe file. In previous versions, when the entry point in shell.map indicates 0001:00000000, it usually implies that the main entry point in shell.exe is at 0x1000. In newer versions, this is not the case. In Visual Studio 8.0 (C++ versions), the executable starts at address 0x400 instead of at 0x1000. As shown in Fig. 4, the AO (shell.exe) is located at **0x00111E00**. The higher 16-bit address 0x0011 indicates that it is loaded above 1 MB to load it in a protected mode memory address.

The lower 16-bit address **0x1E00** is derived as follows. The compiler start address for shell.exe is **0x0000**, but it actually starts at **0x400**. It was observed in the executable that the offset used by this compiler is **0x1e00** more than the actual offset in the executable. Thus, when the executable is relocated at **0x1e00**, the references to the variables were correct as it was generated by the compiler. The main entry point for shell.exe should be at **0x1e00** + **0x400** as shown in Fig. 4. A generic tool is needed to resolve such intricacies involved in generating a memory map for a mass storage device. This tool should consider compiler options, executable formats and map files to create a memory map that is suitable for a given bare machine device.

# VIII. NOVEL FEATURES

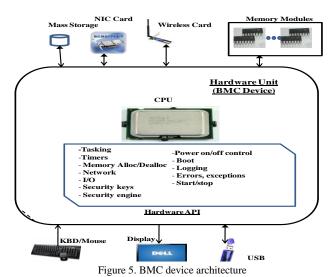

BMC applications provide a new and innovative computer architecture that is based on current trends in technology. Fig. 5 illustrates a vision of future computing. This shows a BMC device that communicates with standard units such as memory, network card, wireless card, USB device, keyboard, mouse, display and mass storage. These units are common to many pervasive devices today. It is thus useful to write computer applications that target the BMC device as a baseline. Each device can run its own native application while using the standard hardware API as illustrated in the figure. All applications can access these interfaces and yet the hardware itself is bare. Until then, we can continue to provide these interfaces as software. The BMC architecture avoids heterogeneity in hardware, software, programming and tools.

# IX. CONCLUSION

We described the BMC paradigm and showed how to build applications based on it. We identified the generic direct bare hardware interfaces needed to eliminate the OS/kernel. The BMC paradigm/approach enables these hardware interfaces to be incorporated in the hardware, thus making the latter more intelligent and able to communicate with the software. The interfaces were used to construct complex bare PC applications that have a small code footprint, are simple to use, provide high performance, and are inherently secure in design. We also presented a bare machine application architecture that enables a BMC device to be used for many pervasive applications. The new paradigm and approach will make it possible to save time, energy, and resources, while reducing the cost of developing applications for each pervasive device. The BMC paradigm demonstrates a new approach to computing based on completely self-supporting applications that eliminate all intermediary software.

### REFERENCES

- [1] P. Appiah-Kubi, R. K. Karne and A.L. Wijesinha, "The Design and Performance of a Bare PC Webmail Server," The 12<sup>th</sup> IEEE International Conference on High Performance Computing and Communications, AHPCC, pp. 521-526, Sept. 2010.

- [2] D. Engler, "The Exokernel Operating Systems Architecture," Dept. of Elec. Eng. and Computer Science, Massachusetts Institute of Technology, Ph.D. Dissertation, 1998.

- [3] FreeBSD/Linux Kernel Cross Reference, http://fxr.watson.org/fxr/source/kern/syscalls.c.

- [4] L. He, R. K. Karne, and A. L. Wijesinha, "Design and Performance of a bare PC Web Server," International Journal of Computer and Applications, vol. 15, pp. 100-112, June 2008.

- [5] R. K. Karne, S. Liang, A. L. Wijesinha and P. Appiah-Kubi, "Bare PC Mass Storage USB Driver," International Journal of Computer and Applications, March 2013.

- [6] R. K. Karne, "Application-oriented Object Architecture: A Revolutionary Approach," 6th International Conference, HPC Asia, Dec. 2002.

- [7] R. K. Karne, V. Jaganathan, T. Ahmed and N. Rosa, "DOSC: Dispersed Operating System Computing," OOPSLA, Onward Track, 20th Annual ACM Conference on Object Oriented Programming, Oct. 2005.

- [8] R. K. Karne, V. Jaganathan and T. Ahmed, "How to run C++ Applications on a bare PC," 6th ACIS International Conference on Software Engineering, Artificial Intelligence, Networking, and Parallel/Distributed Computing (SNPD), pp. 50-55, May 2005.

- [9] G. H. Khaksari, A. L., Wijesinha, R. K., Karne, L., He and S. Girumala, "A Peer-to-Peer Bare PC VoIP Application," IEEE Consumer and Communications and Networking Conference (CCNC), pp. 803-807, Jan. 2007.

- [10] G. H. Khaksari, A. L. Wijesinha, and R. K. Karne, "A Bare Machine Development Methodology," International Journal of Computer Applications, vol. 19, no.1, pp. 10-25, Mar. 2012

- [11] J. Lange. et. al, "Palacios and Kitten: New High Performance Operating Systems for Scalable Virtualized and Native Supercomputing," 24th IEEE International Parallel and Distributed Processing Symposium, Apr. 2010.

- [12] V. S. Pai, P. Druschel and Zwaenepoel, "IO-Lite: A Unified I/O Buffering and Caching System," ACM Transactions on Computer Systems, vol.18 (1), pp. 37-66, Feb. 2000.

- [13] B. Rawal, R. K.Karne, A. L. Wijesinha, "Mini Web Server Clusters for HTTP Request Splitting," IEEE International Conference on High Performance Computing and Communications, pp. 94-100, Sep. 2011.

- [14] M. Schoeberl, S. Korsholm, T. Kalibera and A. P. Ravn, "A Hardware Abstraction Layer in Java," ACM Transactions on Embedded Computing Systems, vol.10, no. 4, Article 42, Nov. 2011.

- [15] S. Soumya, R. Guerin and K. Hosanagar, "Functionality-rich vs Minimalist Platforms: A Two-sided Market Analysis", ACM Computer Communication Review, vol. 41, no. 5, pp. 36-43, Sep. 2011.

- [16] Windows System Call Table, Googlecode.com, retrieved Feb 16, 2012. http://miscellaneuoz.google.com/svn/winsyscall.

# An Orbit Tracking Algorithm in Quantum Systems

Shuang Cong

Dept. Automation

University of Science and Technology of China

Hefei, China

e-mail: scong@ustc.edu.cn

Jianxiu Liu

Dept. Automation

University of Science and Technology of China

Hefei, China

e-mail: zjxliu@mail.ustc.edu.cn

Abstract—A convergence algorithm for the orbit tracking of the free-evolutionary target system in closed quantum system is studied in this paper. The unitary transformation is used to change the problem of orbit tracking into the one of state transferring. The Lyapunov function with a virtual mechanical quantity P is employed to design a Lyapunov-based controller for such a state transferring. The target states are divided into two classes: diagonal and non-diagonal. In the first class, the specific convergent conditions for the target state of diagonal states are studied; in the second class, the target states with non-diagonal superposition states and non-diagonal mixed-states are treated separately by two quite different ways. At last, the system simulation experiments are performed on a two-level quantum system and the tracking process is illustrated on the Bloch sphere.

Keywords-orbit tracking; state transferring; the Lyapunov stability theorem; convergence

# I. INTRODUCTION

In recent years, the closed quantum system control theory has been increasingly developed. Quantum state transferring and quantum system tracking have been fully researched. The effective control algorithm has been designed based on certain control theory, such as optimal control [1-3], Bangbang control [4, 5], the Lyapunov-based control [6-9] and so on. Among them, optimal control produces iterative control algorithm, while bang-bang control is realized experimentally by pulses. Further demand for accuracy may results in the unacceptable number of pulses. The Lyapunov stability theorem may obtain an analytical algorithm, which can help us analyze the characteristics of the system.

In this paper, the quantum system orbit tracking is investigated. For the orbit tracking, the target system is the free-evolutionary of the quantum system to be controlled. What we expect is to make the controlled system track the target system. The control goal is carried on in two steps: firstly, the system orbit tracking problem is changed into the state transferring one; secondly, a convergent control algorithm is designed to complete the goal.

In fact, the control algorithm designed by the Lyapunov stability theorem is only stable, which cannot guarantee the quantum system converges to desired target state. For this purpose, a convergent rather than just stable control algorithm is needed to manipulate the quantum system. Some papers on this topic have been reported [9, 10]. Among them, complete state transferring with target state of eigenstates and diagonal mixed-states in closed quantum

system has been proved to be convergent conditionally [11, 12]. However, there is an open problem on the convergence of the non-diagonal target states including the superposition states and some mixed-states. In [12], a Lyapunov function based on virtual mechanical quantity P was proposed to get the convergence conditions for the diagonal mixed-states. However, it did not give specific instructions on how to design P. We will discuss the detailed convergence conditions of diagonal target states and non-diagonal target states in this paper.

The rest of the paper is organized as follows. In Section II, the system model is described by the Liouville equation. The Lyapunov stability theorem is used to design the trajectory tracking control algorithm in Section III. Section IV is divided into two parts, the first part is to handle the convergence of initial target state with diagonal mixes-state and the second part is the one for non-diagonal initial target state. In Section V, numerical simulation experiments are performed on a two-level system. Finally, Section VI concludes this paper.

# II. DESCRIPTION OF THE CONTROL SYSTEM MODEL

In this paper, we use quantum-Liouville equation to describe the control system model

$$i\hbar\frac{\partial}{\partial t}\hat{\rho}(t) = \left[H_0 + \sum_m f_m(t)H_m, \hat{\rho}(t)\right]\hat{\rho}(0) = \hat{\rho}_0 \qquad (1a)$$

$$i\hbar \frac{\partial}{\partial t} \hat{\rho}_f(t) = \left[ H_0, \hat{\rho}_f(t) \right] \quad \hat{\rho}_f(0) = \hat{\rho}_{f0} \quad (1b)$$

where  $H_0$  is the free Hamiltonian representing the energy of the system and  $H_m$  represent system's control Hamiltonians, all of them will be assumed to be time-independent.  $f_m(t)$  are time-dependent external control fields. The Planck constant is chosen as  $\hbar=1$  for convenience. The system state is denoted by density matrix  $\hat{\rho}(t)$ , the initial states of which at t=0 is  $\hat{\rho}_0$ . Similarly,  $\hat{\rho}_f(t)$  is the target system state and its initial value is  $\hat{\rho}_{f0}$ .

The control objective is to design a convergent control algorithm to make the state  $\hat{\rho}(t)$  of (1a) follow target state  $\hat{\rho}_f(t)$  of system (1b).

Firstly, to change the orbit tracking problem into a state transferring one, a unitary transformation  $U(t) = \exp(-itH_0)$  is performed on system (1):  $\rho(t) = U^{\dagger}(t) \hat{\rho}(t) U(t)$ ,  $\rho_f(t) = U^{\dagger}(t) \hat{\rho}_f(t) U(t)$ , where "†" denotes conjugate transpose, "^" denotes states before unitary transformation. The system (1) after this transformation is represented by

$$i\frac{\partial}{\partial t}\rho(t) = \left[\sum_{m} f_m(t)H_m(t), \rho(t)\right] \quad \rho(0) = \hat{\rho}_0 \quad (2a)$$

$$i\frac{\partial}{\partial t}\rho_f(t) = 0$$

$\rho_f(0) = \hat{\rho}_{f0}$  (2b)

where  $H_m(t) = U^{\dagger}(t)H_mU(t)$ . Calculate (2b), one gets

$$\rho_f(t) = \hat{\rho}_{f0}. \tag{3}$$

After the above transformation, we have changed the tracking problem into the state transferring one. At present, the control goal of system (1a) following target system (1b) becomes the one of regulating state of (2a) to target state (3).

# III. CONTROL ALGORITHM DERIVATION

Among many control methods, the Lyapunov-based method is simpler and easy to design. The basic idea of the Lyapunov method is to select a Lyapunov function V(x) which satisfies the following three conditions: a) V(x) is continuous and its first-order partial derivatives is also continuous in its definition; b) V(x) is positive semi-definite, i.e.,  $V(x) \ge 0$ ; c) The first order time derivative of the Lyapunov function is negative semi-definite, i.e.,  $\dot{V}(x) \le 0$ .

There are usually three kinds of Lyapunov functions [11]. Here, the Lyapunov function based on virtual physical quantity is chosen

$$V(\rho) = tr(P\hat{\rho}), \tag{4}$$

where P is virtual physical observable operator.

To obtain a convergent control algorithm, the first-order time derivation of function (4) is obtained as

$$\dot{V} = -\sum_{m} f_m(t) tr(iH_m(t)[\rho(t), P]). \tag{5}$$

For the sake of simplicity and availability, we let each item on the right side of (5) of summation sign be non-positive in order to ensure  $\dot{V} \leq 0$ . The control algorithm can be derived as

$$f_m(t) = -k_m tr\left(iH_m\left(t\right)\left(\left[\rho(t), P\right]\right)\right), \ k_m > 0 \tag{6}$$

where,  $k_m > 0$  is the control gain to adjust the convergence speed of the system state.

Comparing system (1) with (2a) and (3), one can see that: the system (1) is autonomous and the system (2) is not, however, the time-dependent target state  $\rho_f(\iota)$  in (1b) becomes a stationary state  $\hat{\rho}_{f0}$  in (3).

As we know, the control algorithm (6) designed by the Lyapunov stability theorem is usually only a stable one, which can not guarantee that the system converges to target state. For this reason, we need to do further study to get the convergence condition  $\dot{V} < 0$ , which may guide people to design a convergent control algorithm. Next, we study this problem in detail.

# IV. CONTROL ALGORITHM CONVERGENCE ANALYSIS

In order to implement effective control on a quantum system, a convergent control algorithm is even more important than the control algorithm itself. In the process of state transferring, the desired target is a time-invariant state. The variety of quantum states such as eigenstates, superposition states and mixed-states makes the different expressions of target state. On the one hand, from the system control perspective, the initial state of target system will be grouped into stationary state and the non-stationary one. For the stationary target state, according to (1b),

$$i\hbar \frac{\partial}{\partial t} \hat{\rho}_f(t) = 0$$

holds, and so does  $\hat{\rho}_f(t) = \hat{\rho}_f(0)$ . In such

a case, one can get  $\left[H_0,\hat{\rho}_f\left(0\right)\right]$ =0. The system tracking of (1a) is equivalent to the state transferring. For the non-stationary initial target state, the unitary transformation has changed the tracking problem into the state transferring one. Therefore, we can always change the system tracking into the state transferring. On the other hand, from the convergence of view, the initial target states are divided into two kinds. The first one is diagonal initial target state including eigenstates and some mixed-states. It can be represented by a diagonal density matrix. The second kind is non-diagonal initial target state, including superposition state and some mixed-states, whose convergence has not been resolved fully so far.

For autonomous system (1), the LaSalle's invariant principle can be used to analyze the convergence, where two assumptions are needed [13]: Assumption 1:  $H_0$  is strongly regular, i.e., all the transition frequencies (differences of pairs of energy levels) are different, viz.  $\Delta_{jk} \neq \Delta_{pq}$ ,  $(j,k) \neq (p,q)$ , where  $\Delta_{jk} = \lambda_j - \lambda_k$  and  $\lambda_j$  is an

eigenvalues of  $H_0$ . Assumption 2: Control Hamiltonian full-connected.  $H_{m}$  $H_m \in \{ \hbar h_{ik} \mid h_{ik} = |j\rangle\langle k| + |k\rangle\langle j|, j > k \}$ , where  $|j\rangle$  is the eigenstate associated with  $\lambda_i$  . Because of the unitary evolution of closed quantum system, if being reachable then target state must be unitarily equivalent to the initial state, i.e., there exists a unitary transformation U such that  $\hat{\rho}_0 = U \hat{\rho}_{f0} U^{\dagger}$ . We make it as Assumption 3.

The LaSalle's invariant principle is not able to deal with the non-autonomous system (2), however, the Barbalat lemma can be applied based on above three assumptions, whose content is [14]: If scalar function V(x,t) satisfies: (1) V(x,t) is lower bounded; (2)  $\dot{V}(x,t)$  is negative semidefinite; (3)  $\dot{V}(x,t)$  is uniformly continuous in time, then  $\dot{V}(x,t) \to 0$  as  $t \to \infty$ . One can see from the Lyapunov function (4) that (4) satisfies all the three conditions of Barbalat lemma: (1)  $V = tr(P\rho) \ge 0$  is lower bounded for a positive P; (2) Its first order derivative is negative semidefinite under control algorithm (6); (3) The third condition can be replaced by the existence and continuity of the derivation  $\ddot{V}\left(\rho,t\right) = -\sum_{m} f_{m}\left(t\right) \left\{ tr\left(i\dot{H}_{m}(t)[\rho,P]\right) + tr(iH_{m}(t)[\dot{\rho},P]) \right\}$

is bounded for a bounded input.

According to the Barbalat Lemma, the first derivation of the Lyapunov function converges to zero for  $t \to \infty$ , viz.,  $\dot{V}(\rho(\infty),\infty)=0$ . So a limitation states set at  $t\to\infty$  is deduced by the Barbalat Lemma. We defined it as a stable set  $\mathcal{R}$  , which is a concept similar to invariant set. According to the formula (6), the states in stable set satisfy f=0. For the non-autonomous system (2), if  $\rho \in \mathbb{R}$ , then  $\dot{\rho}$ =0 holds for f=0. It means that, once the system evolves into the stable set, it will stop at this set.

The stable set R is the set of critical points on any dynamic trajectory, viz.

$$\mathcal{R} \equiv \left\{ \rho_s : tr(iH_m(t)[\rho_s, P]) = 0, \forall m, t \right\}, \tag{7}$$

where  $\rho_s$  denote critical stable points of (2), and  $\rho_f \in \mathbb{R}$ . The controlled system may converge to any one of states in stable set  $\mathcal{R}$ . Now P is to be constructed to make the system converge to the target state. According to Assumption 2, (7) is rewritten as  $\Re = \{ \rho_s : [\rho_s, P] = D \}$ , where D is a diagonal matrix. Obviously, if P is chosen as a diagonal matrix, D is zero one, otherwise we can always design a set of proper eigenvalues of P to simplify (7) as [15]:

$$\mathcal{R} = \left\{ \rho_s : [\rho_s, P] = 0 \right\}. \tag{8}$$

Equation (8) is the stable set to be discussed in this paper. It is known that (4) is a function of state and the system (2) will converge to stable set (8). Whether the system converges to target state or not depends on the relative position among target state, the controlled initial state, and all other stable states than target state. To make the system converge to the target state, the following condition is needed, viz. the relationship among initial state, target state, and other stable states must satisfy [12]

$$v(\rho_f) < v(\rho_0) < v(\rho_s). \tag{9}$$

Equation (9) is the condition to ensure the convergence of the controlled system. How to realize (9) is another key point which needs to be solved. In the following we'll focus on this topic by designing the suitable P. The solutions are given by two cases.

# A. The target state is diagonal mixed-state

The convergent conditions for diagonal target states have been investigated adequately [11-13]. However, the concrete construction of P has not been mentioned in previous results. In this section, we'll discuss how to design *P* in (4) to satisfy (9).

Suppose the target state  $\rho_f$  is a diagonal target state and  $\{\lambda_i, i=1,2\cdots n\}$  is the eigen-spectrum of  $\rho_0$ . The target state  $\rho_f$  should be one permutation of  $\{\lambda_i, i = 1, 2 \cdots n\}$ , viz.  $\rho_f = diag(\lambda_1, \lambda_2 \cdots \lambda_n)$ . The other states  $\rho_s$  in  $\mathcal{R}$  are the different permutations of eigen-spectrum. In order to construct a *P* satisfied (9), three steps are performed:

Firstly, P is constructed to make  $\rho_f$  be the point corresponding to the minimum value of (4), which is realized by the following lemma:

1: If the diagonal target state  $\rho_f = diag(\lambda_1, \lambda_2 \cdots \lambda_n)$ , the matrix P corresponding to  $\rho_f$ is  $P = diag(p_1, p_2, \dots p_n)$ , then  $\rho_f$  is the point for the Lyapunov function (4) to be the minimum if the diagonal element  $p_i$  of P meets  $(\lambda_i - \lambda_j)(p_i - p_j) < 0, \forall i \neq j$ .

The proof of Lemma 1 is in Appendix 1.

Secondly, based on Lemma 1, a further study on P is carried out and (9) is divided into two parts:

Part 1:

$$v(\rho_f) < v(\rho_0)$$

The condition  $v(\rho_f) < v(\rho_0)$  indicates that Lyapunov function value of initial state is larger than that of target state. Otherwise it is inconsistent with the monotonically decreasing of (4) and the target state will be unreachable. is easy obtain  $v(\rho_f)-v(\rho_0)=\sum_{i=1}^n(P)_{ii}\left(\lambda_i-(\rho_0)_{ii}\right) \quad \text{Based} \quad \text{on the relationship between eigenvalues and matrix diagonal elements, the expression } \sum_{i=1}^n\lambda_i=\sum_{i=1}^n\mu_i=\sum_{i=1}^n(\rho_0)_{ii}=1 \text{ holds,}$  where  $(\rho_0)_{ii}$  is the i-th diagonal element of the initial state  $\rho_0$ . So there must be at least one k to make  $\lambda_k<(\rho_0)_{kk}$  hold. If one wants to make  $v(\rho_f)-v(\rho_0)=(P)_{kk}\left(\lambda_k-(\rho_0)_{kk}\right)+\sum_{i=1,i\neq k}^n(P)_{ii}\left(\lambda_i-(\rho_0)_{ii}\right)<0$  hold, where  $(P)_{kk}$  is the k-th diagonal element of P, then we choose a certain k satisfied  $\lambda_k<(\rho_0)_{kk}$ , one gets

$$(P)_{kk} > \sum_{i=1,i\neq k}^{n} (P)_{ii} \left(\lambda_i - (\rho_0)_{ii}\right) / \left((\rho_0)_{kk} - \lambda_k\right). (10)$$

Maybe there are more than one k to satisfy  $\lambda_k < (\rho_0)_{kk}$ , we usually choose the one which makes  $(P)_{kk}$  correspond to a larger value such that  $v(\rho_f) < v(\rho_0)$  holds.

Part 2:

$$v(\rho_0) < v(\rho_s)$$

$ho_s$  should be one of the permutations of eigen-spectrum. According to Assumption 3,  $ho_0=U

ho_fU^\dagger$ , so one has

$$tr(P\rho_{0}) = tr(PU\rho_{f}U^{\dagger}) = \sum_{i=1}^{n} (P)_{ii} \sum_{j=1}^{n} (\rho_{f})_{jj} (U_{ij})^{2}$$

$$tr(P\rho_{s}) = \sum_{i=1}^{n} (P)_{ii} (\rho_{s})_{ii}$$

$$tr(P\rho_{0}) - tr(P\rho_{s}) = \sum_{i=1}^{n} (P)_{ii} \left(\sum_{j=1}^{n} (\rho_{f})_{jj} (U_{ij})^{2} - (\rho_{s})_{ii}\right)$$

$\rho_s$  and  $\rho_f$  have the same spectrums, there must be  $\left(\rho_f\right)_{kk} = \left(\rho_s\right)_{ii}$ . For any unitary matrix U, there exist  $UU^{\dagger} = U^{\dagger}U = I$  and  $\sum_{j=1}^{n} \left(U_{ij}\right)^2 = 1$ . So one can get  $tr(P\rho_0) - tr(P\rho_s) = \sum_{i=1}^{n} \left(P\right)_{ii} \left(\sum_{j \neq k}^{n} \left(\rho_f\right)_{jj} \left(U_{ij}\right)^2 - \left(\rho_f\right)_{kk} \sum_{j \neq k}^{n} \left(U_{ij}\right)^2\right) \\

= \sum_{i=1}^{n} \left(P\right)_{ii} \sum_{i=1}^{n} \left(\left(\rho_f\right)_{jj} - \left(\rho_f\right)_{kk}\right) \left(U_{ij}\right)^2$

For the above equation, there is at least one l to make  $\left(\rho_f\right)_{ll}-\left(\rho_f\right)_{kk}<0$  hold. To make  $tr(P\rho_0)-tr(P\rho_s)<0$ , the following expression is needed

$$(P)_{ll} > \left(\sum_{i \neq l}^{n} (P)_{ii} \sum_{j \neq k}^{n} \left( \left( \rho_{f} \right)_{jj} - \left( \rho_{f} \right)_{kk} \right) \left( U_{ij} \right)^{2} + \left( P \right)_{ll} \bullet$$

$$\sum_{j \neq k, j \neq l}^{n} \left( \left( \rho_{f} \right)_{jj} - \left( \rho_{f} \right)_{kk} \right) \left( U_{lj} \right)^{2} \right) / \left( \left( \rho_{f} \right)_{kk} - \left( \rho_{f} \right)_{ll} \right)$$

$$(11)$$

The above process is to construct P for diagonal target states. We conclude that: if the target state is of diagonal, a Hermite and positive diagonal matrix P is selected. To ensure the convergence, the diagonal elements of P must satisfy Lemma 1, (10) and (11) simultaneously.

# B. The target state is of non-diagonal density matrix

It is more complicated to analyze the convergence for the non-diagonal target state. The idea is as follows: let the non-diagonal target state be changed into diagonal one and the virtual physical quantity P is designed as that in A. However, the superposition state is one kind of pure states, which can be represented by wave functions as  $\rho_f = \left| \psi_f \right\rangle \left\langle \psi_f \right|$ . In this case, the diagonalization of target state is not necessary. Next, we go onto the analysis of non-diagonal superposition state and mixed-state in detail.

1) In the case of non-diagonal superposition state

Prior to analysis, another lemma is introduced.

Lemma 2 [16]: For the *n*-level Hermite matrix *A* and *B*, if they are commutive, viz. [A, B] = 0, then *A* and *B* own the same eigenstates. We rewrite *P* according to its eigendecomposition as  $P = \sum_{k} p_k |\psi_k\rangle \langle \psi_k|$ , where  $|\psi_k\rangle$  is its

eigenstate and  $p_k$  is eigenvalue. According to  $\rho_f \in \mathbb{R}$  and **Lemma 2**: P is demonstrated as

$$P = p_1 \left| \psi_f \right\rangle \left\langle \psi_f \right| + \sum_{k=2}^n p_k \left| \psi_k \right\rangle \left\langle \psi_k \right|, \text{ where } \left| \psi_1 \right\rangle = \left| \psi_f \right\rangle. \text{ And } \left\langle \psi_i \middle| \psi_j \right\rangle = 0, \text{ for } i \neq j.$$

$$(12)$$

And  $\rho_s$  should be

$$\rho_{s} = \lambda_{1} \left| \psi_{f} \right\rangle \left\langle \psi_{f} \right| + \sum_{k=2}^{n} \lambda_{k} \left| \psi_{k} \right\rangle \left\langle \psi_{k} \right| \quad \sum_{k=1}^{n} \lambda_{k} = 1 \quad (13)$$

It is known that the states  $\rho_0$  and  $\rho_s$  have the same spectrum under the unitary evolution, and therefore  $\rho_s$  has the same eigenvalues with  $\rho_0$ , so does the target state  $\rho_f$ .

Substituting  $\rho_f = \left| \psi_f \right\rangle \left\langle \psi_f \right|$  into (13), the eigenspectrum of  $\rho_f$  is  $\{1,0,\cdots 0\}$ . Then for  $\rho_s$ , there is only one eigenvalue  $\lambda_i$  to be non-zero, viz.  $\rho_s = \lambda_i \left| \psi_i \right\rangle \left\langle \psi_i \right| \; (\lambda_i = 1)$ .

If it denotes  $\rho_j = |\psi_j\rangle\langle\psi_j|$  in (12), then

$$\begin{cases} v(\rho_f) = tr(P\rho_f) = p_1 \\ v(\rho_0) = p_1 tr(\rho_f \rho_0) + \sum_{k=2}^n p_k tr(\rho_k \rho_0) \\ v(\rho_s) = p_j \quad (j \neq 1) \end{cases}$$

(14)

Combined (14) with (9), a suitable P must be constructed to satisfy

$$0 < p_1 < p_1 tr(\rho_f \rho_0) + \sum_{k=2}^n p_k tr(\rho_k \rho_0) < p_j (j \neq 1) \quad (15)$$

It can be seen from (15) that the virtual mechanical quantity P may not be a diagonal matrix for non-diagonal superposition target state. The P constructed based on (12) and (15) can guarantee the convergence of non-diagonal superposition target state, where (12) describes how to construct the eigenstates and (15) is to determine the eigenvalues. Moreover, the eigenvalue  $p_1$  of P, whose corresponding eigenstate is the target state, is the smallest one

# 2) In the case of non-diagonal mixed-state

For system (1), suppose the initial target state  $\hat{\rho}_{f0}$  is a non-diagonal mixed-state. The solution of (1b) is  $\hat{\rho}_f(t) = e^{-iH_0t}\hat{\rho}_{f0}e^{iH_0t}$ . To deal with this situation, a unitary transformation has transformed the tracking problem of (1) into the state transferring one of (2). We follow the idea of changing the non-diagonal  $\hat{\rho}_{f0}$  into a diagonal one by another unitary transformation and then a convergent control algorithm can be designed based on A.

In system (2), the target state  $\hat{\rho}_{f0}$  is a Hermite matrix, so it exists another unitary transformation  $U_f$  to meet  $U_f\hat{\rho}_{f0}U_f^{\dagger}=D_f$ . It is performed on system (2), viz.,  $\rho'=U_f\rho U_f^{\dagger}$ ,  $\rho'_f=U_f\rho_f U_f^{\dagger}=D_f$ , then the system (2) becomes

$$i\hbar\frac{\partial}{\partial t}\rho'(t) = \left[H_0 + \sum_{m=1}^{M} f_m(t)H_{mt}, \rho'(t)\right] \rho'(0) = U_f \hat{\rho}_0 U_f^{\dagger}$$

(16a)

$$i\hbar \frac{\partial}{\partial t} \rho_f'(t) = 0 \qquad \rho_f'(0) = D_f \tag{16b}$$

where  $H_{mt} = U_f H_m U_f^{\dagger}$ .

After unitary transformation  $U_f$ , the tracking of target system with non-diagonal initial state  $\hat{\rho}_{f0}$  in (2) can be changed into the tracking of a diagonal stationary state in (16). According to (8), the stable set of (16) is still  $\mathcal{R} \equiv \{\rho_s: [\rho_s, P] = 0\}$ . The convergence analysis is the same as that in A.

In conclusion, we have acquired the convergence conditions for non-diagonal target states.

# V. APPLICATIONS AND EXPERIMENTAL RESULTS ANALYSES

In this part, a two level atom system controlled by a single control field is considered. Take superposition target state for example, the effectiveness of the proposed method will be illustrated.

The free Hamiltonian of the controlled system (1) is  $H_0=\omega\sigma_z$  and the control Hamiltonian is  $H_1=\sigma_x$ , where  $\sigma_i(i=x,y,z)$  denotes Pauli matrix and  $\sigma_x=\begin{bmatrix}0&1;1&0\end{bmatrix}$ ,  $\sigma_z=\begin{bmatrix}1&0;0&-1\end{bmatrix}$ . Obviously, this example satisfies the three conditions in Section IV.

The initial state of (1a) is  $|\psi_0\rangle = \frac{1}{\sqrt{3}}|0\rangle + \frac{\sqrt{2}}{\sqrt{3}}|1\rangle$  and the initial target state of (1b) is  $|\psi_f\rangle = \frac{1}{\sqrt{8}}|0\rangle + \frac{\sqrt{7}}{\sqrt{8}}|1\rangle$ . They are both non-diagonal superposition states. The design process of a convergent control algorithm is as follows:

# 1) Construct P

To construct P, a set of linearly independent vector  $|\psi_k\rangle(k=1,2)$  is prepared. In this example, we choose  $|\psi_1\rangle=|\psi_f\rangle$ ,  $|\psi_2\rangle=e_1$ . Then the Schmidt orthogonalization is performed. Suppose the orthogonalized vectors are  $|s_1\rangle$  and  $|s_2\rangle$ , where  $|s_1\rangle=|\psi_f\rangle$ . According to (12),  $P=p_1|s_1\rangle\langle s_1|+p_2|s_2\rangle\langle s_2|$  holds. The state except target state in  $\mathcal R$  is  $\rho_s=|s_2\rangle\langle s_2|$ . Here, we choose  $p_1=0.2, p_2=2$ , then  $P=[1.775 \ -0.595; -0.595 \ 0.425]$ .

# 2) System Simulation results

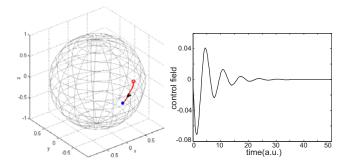

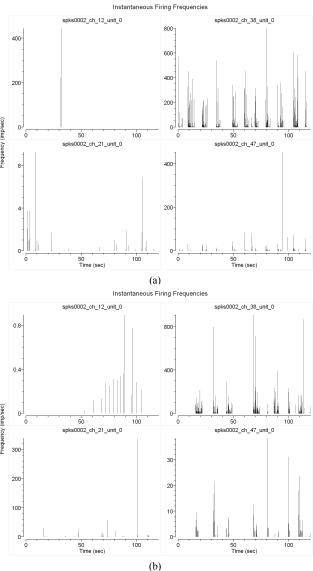

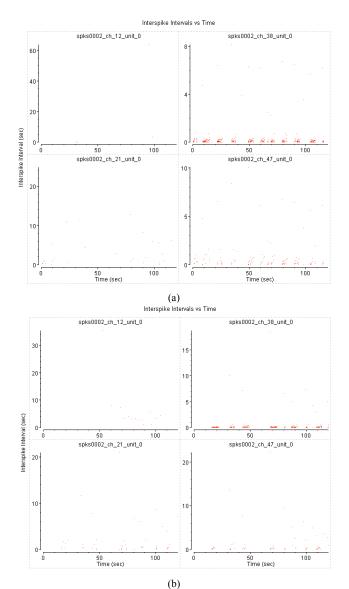

The control gain in (6) is selected as k = 0.1. The simulation results are showed in Fig. 1, where the red circle denotes the controlled initial state and the blue circle is the target state; the red line is the controlled trajectory and the arrow indicates its direction. Fig. 1(a) shows the state transferring process during  $t \in [0,50]$ . Fig. 1(b) is the control field.

To illustrate better the control strategy, the control field Fig. 1(b) is applied to the original system (1). The tracking results are showed in Fig. 2, where the red dashed line is the evolution curve of controlled state in (1a) and the blue solid line is the one of target state in target system (1b); the red circle and the blue circle indicate the initial location at the current period of the controlled state and the target state respectively; the arrow indicates the direction. In Fig. 2(a), the evolution trajectory at  $t \in [0,8]$  is showed, from which one can see that the controlled system is asymptotically stable with respect to the target system on the Bloch sphere. Fig. 2(b) is the state trajectory at  $t \in [8,30]$  and Fig. 2(c) is the magnified bottom view of Fig. 2 (b). We have specially labeled the different locations with black box. It can be seen

Figure 1(a). State evolution of (2)

Figure 1(b). Control field

Figure 2. The state trajectory tracking process of non-diagonal superposition target state

from Fig. 2(c) that the red circle overlapped the blue one at t=30 (the top box), so the tracking is completed at the moment. Since then, the controlled system would follow the target state in the target orbit. All the three figures demonstrated completely how the system (1a) to track the system (1b). If the index performance  $v = \|\hat{\rho}(t) - \hat{\rho}_f(t)\|^2 = tr\Big((\hat{\rho} - \hat{\rho}_f)^{\dagger}(\hat{\rho} - \hat{\rho}_f)\Big)$  is used to

measure the tracking accuracy, then  $v = 9.41*10^{-5}$  holds at t=50.

In summary, for the initial target states including diagonal and non-diagonal target states, the controlled system will converge to its target system under the control algorithm (6) with P designed as in Section IV.

# VI. CONCLUSION

We have proposed a convergent orbit tracking control algorithm for the free-evolutionary target quantum system in

this paper. The unitary transformation was used to change the tracking problem into the regulation one. For the convergence analysis in state regulation, the target states were divided into diagonal and non-diagonal ones. For the former, we continued to perfect the convergence analysis of diagonal mixed-states. The explicit convergence conditions of P have been obtained. For the non-diagonal target state, if the superposition state was considered, a specific non-diagonal P was designed to ensure the convergence. If the target state was non-diagonal mixed-state, there must be a unitary transformation to change the Hermitian non-diagonal matrix into the diagonal one, and the convergence conditions could been obtained as that of diagonal mixed-state.

Appendix 1: The proof of Lemma 1.

Prove: P is a diagonal matrix, one gets  $\dot{v}(\rho_f) = 0$  from (10).

$$\ddot{v}(\rho) = -i * \sum_{m} f_{m} \left\{ tr(\dot{H}_{mt}[\rho, P]) + tr(H_{mt}[\dot{\rho}, P]) \right\}$$

$$\ddot{v}(\rho_{f}) = - \sum_{m} f_{m}^{2} tr([H_{mt}, \rho_{f}] * [P, H_{mt}])$$

$$= \sum_{m} f_{m}^{2} tr([H_{mt}, \rho_{f}] * [H_{mt}, P])$$

$$\text{Let} \qquad A = [H_{mt}, \rho_{f}], B = [H_{mt}, P] \qquad , \qquad \text{then}$$

$$(A)_{ij} = (\lambda_{j} - \lambda_{i})(H_{mt})_{ij}, (B)_{ij} = (p_{j} - p_{i})(H_{mt})_{ij}, \text{ so}$$

$$tr(AB) = \sum_{i=1}^{n} \sum_{j=1}^{n} A_{ij}B_{ji} = \sum_{i=1}^{n} \sum_{j=1}^{n} (\lambda_{j} - \lambda_{i})(p_{i} - p_{j})(H_{mt})_{ij}^{2}$$

$$= -\sum_{i=1}^{n} \sum_{j=1}^{n} (\lambda_{j} - \lambda_{i})(p_{j} - p_{i})(H_{mt})_{ij}^{2}$$

If  $\rho_f$  is a stable state, then  $\ddot{v}(\rho_f) > 0$ , one gets:  $(\lambda_i - \lambda_j)(p_i - p_j) < 0, \forall i \neq j$ .

Let  $\{\mu_1, \mu_2 \cdots \mu_n\}$  be the spectrum of  $\rho_f$  with  $\mu_i$  arranged in a non-increasing order, viz  $\mu_1 < \mu_2 < \cdots < \mu_n$ . Then the corresponding P is  $P = diag\left(p_1, p_2, \cdots p_n\right)$  and  $p_1 > p_2 > \cdots > p_n$  is obtained by the above description. Any other states  $\rho_s$  in stable set  $\mathcal R$  can be obtained by m times swapping arbitrary two elements of  $\{\mu_1, \mu_2 \cdots \mu_n\}$ . We let  $bool = tr(P\rho_f) - tr(P\rho_s)$ .

Suppose the spectrum from smallest to largest of target state is  $\left\{\mu_1,\mu_2,\cdots,\mu_i,\cdots,\mu_j,\cdots,\mu_k,\cdots\mu_n\right\}$ , then:

$$i \leftrightarrow j$$

:

$$\begin{aligned} bool &= p_i \left( \mu_i - \mu_j \right) + p_j \left( \mu_j - \mu_i \right) = \left( p_i - p_j \right) \left( \mu_i - \mu_j \right) < 0 \\ i &\longleftrightarrow j, j &\longleftrightarrow k : \end{aligned}$$

$$bool = p_{i}(\mu_{i} - \mu_{j}) + p_{j}(\mu_{j} - \mu_{k}) + p_{k}(\mu_{k} - \mu_{i})$$

$$= p_{i}(\mu_{i} - \mu_{j}) + p_{j}(\mu_{j} - \mu_{i} + \mu_{i} - \mu_{k}) + p_{k}(\mu_{k} - \mu_{i})$$

$$= (p_{i} - p_{j})(\mu_{i} - \mu_{j}) + (p_{j} - p_{k})(\mu_{i} - \mu_{k}) < 0$$

$$i \leftrightarrow j, j \leftrightarrow k, k \leftrightarrow l :$$

$$bool = p_{i}(\mu_{i} - \mu_{j}) + p_{j}(\mu_{j} - \mu_{k}) + p_{k}(\mu_{k} - \mu_{l}) + p_{l}(\mu_{l} - \mu_{i})$$

$$= p_{i}(\mu_{i} - \mu_{j}) + p_{j}(\mu_{j} - \mu_{i} + \mu_{i} - \mu_{k})$$

$$+ p_{k}(\mu_{k} - \mu_{i} + \mu_{i} - \mu_{l}) + p_{l}(\mu_{l} - \mu_{i})$$

$$= (p_{i} - p_{j})(\mu_{i} - \mu_{j}) + (p_{j} - p_{k})(\mu_{i} - \mu_{k}) + (p_{k} - p_{l})(\mu_{i} - \mu_{l}) < 0$$

and so on. Finally, we get  $v(\rho_{f}) < v(\rho_{s})$ . Lemma 1 is proved.

### ACKNOWLEDGMENT

This work was supported in part by the National Key Basic Research Program under Grants No. 2011CBA00200, the National Science Foundation of China under Grant No. 61074050.

# REFERENCES

- [1] A. P. Peirce, M. A. Dahleh, and H. Rabitz, "Optimal control of quantum-mechanical systems: Existence, numerical approximation, and applications", Physical Review A, Vol. 37, No. 12, Jun. 1988, pp. 4950–4964, doi: 10.1103/PhysRevA.37.4950.

- [2] S. Cong, Y. Zhang, and K. Li, "Optimal control of mixed-state quantum systems based on Lyapunov method", Biosignals, Rome, 2011, pp. 22-30.

- [3] M. Sugawara, "General formulation of locally designed coherent control theory for quantum system", Journal of Chemical Physics, Vol. 118, No. 15, Apr. 2003, pp. 6784-6800, doi:10.1063/1.1559680.

- [4] J. R. West, D. A. Lidar, B. H. Fong and M. F. Gyure, "High fidelity quantum gates via dynamical decoupling", Physical Review Letter, Vol. 105, No. 23, Dec. 2010, pp. 230503: 1-4, doi: 10.1103/PhysRevLett.105.230503.

- [5] X. Peng, D. Suter, and D. A. Lidar, "High fidelity quantum memory via dynamical decoupling: theory and experiment",

- Journal of physics B: Atomic, Molecular and Optical Physics, Vol. 44, July 2011, pp. 154003: 1-6, doi:10.1088/0953-4075/44/15/154003.

- [6] J. Liu and S. Cong, "Trajectory Tracking of Quantum States based on Lyapunov method", The 9th IEEE International Conference on Control & Automation (ICCA 11), Santiago, Dec. 2011, pp.318-323, doi: 10.1109/ICCA.2011.6137903.

- [7] M. Mirrahimi, G. Turinici, and P. Rouchon, "Reference Trajectory Tracking for Locally Designed Coherent Quantum Controls", Journal of Physical Chemistry A, Vol. 109, No. 11, 2005, pp. 2631-2637, doi: 10.1021/jp0472461.

- [8] K. Beauchard, J. Coron, M. Mirrahimi, and P. Rouchon, "Implicit Lyapunov control of finite dimensional schrodinger equations", Systems & Control Letters, Vol. 56, 2007, pp.388-395, doi:10.1016/j.sysconle.2006.10.024.

- [9] M. Mirrahimi, P. Rouchon, and G. Turinici, "Lyapunov control of bilinear Schrodinger equations", Automatica, vol. 41, Aug. 2005, pp. 1987-1994, doi: 10.1016/j.automatica.2005.05.018.

- [10] M. Mirrahimi and P. Rouchon, "Trajectory tracking for quantum systems: a Lyapunov approach", Proc. International Symposium MTNS, 2004, pp. 1-6.

- [11] K. Sen and S. Cong, "Population control on equilibrium states of quantum systems via Lyapunov method", Acta Automatica Sinica, Vol. 36, No. 9, Sep. 2010, pp. 1257-1263, doi: 10.1016/S1874-1029(09)60052-5.

- [12] S. Kuang and S. Cong, "Lyapunov stabilization strategy of mixed-state quantum systems with ideal conditions", Control and Decision, Vol. 25, No. 2, Feb. 2010, pp. 273-277.

- [13] J. LaSalle and S. Lefschetz, Stability by Lyapunov's Direct Method with Applications, 1rd ed., New York: Academic Press, 1961, pp. 56-60.

- [14] M. Hou, G. Duan and M. Guo, "New versions of Barbalat's lemma with applications", Journal of Control Theory & Application, Vol. 8, Iss. 4, No. 2010, pp. 545-547, doi: 10.1007/s11768-010-8178-z.

- [15] S. Cong and J. Liu, "Orbit Tracking Control of Quantum Systems", arXiv:1211.5447v2,17 Jan 2013

- [16] R. I. Karasik, K. P. Marzlin, B. C. Sanders, and K. Birgitta Whaley, "Criteria for dynamically stable decoherenec-free subspace and incoherently generated Coherences", Physical Review A, Vol. 77, No. 5, 2008, pp. 052301: 1-12, doi: 10.1103/PhysRevA.77.052301.

# **Face Recognition Using 1DLBP Texture Analysis**

Amir Benzaoui and Abdelhani Boukrouche

Laboratory of Inverses Problems, Modeling, Information and Systems (PI:MIS)

Department of Electronics and Telecommunication

University of 08 Mai 1945

P.O box 401, Guelma, Algeria

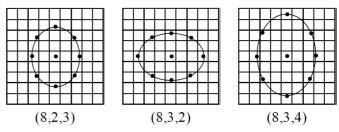

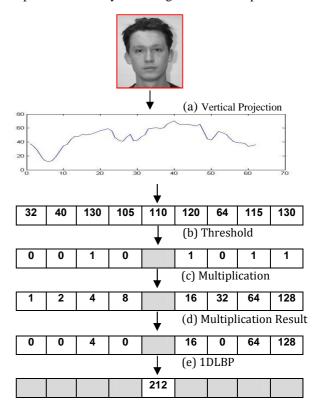

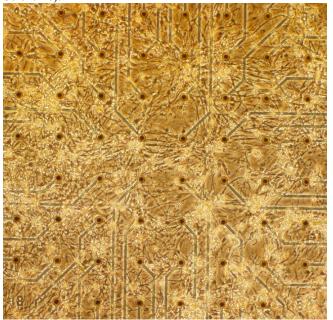

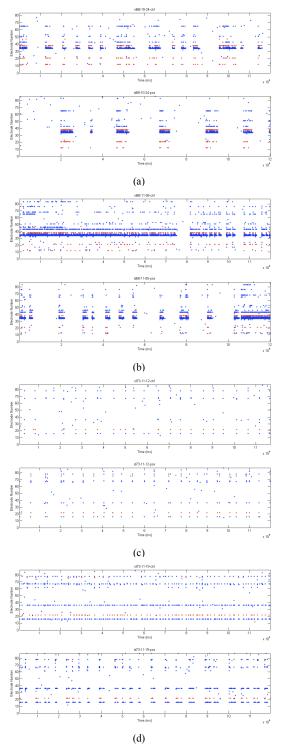

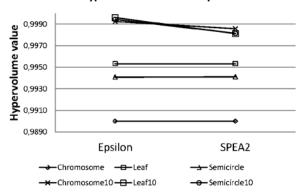

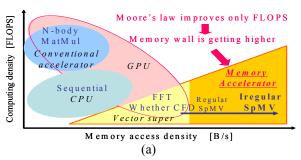

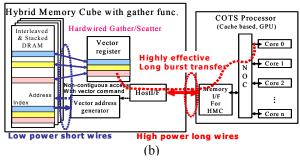

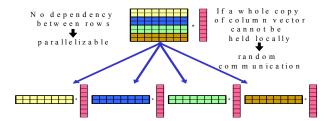

amirbenzaoui@gmail.com abdelhanib@yahoo.fr