# **CENICS 2015**

The Eighth International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-430-5

August 23 - 28, 2015

Venice, Italy

## **CENICS 2015 Editors**

Falk Salewski, Muenster University of Applied Sciences, Germany

Sergey Yurish, IFSA, Spain

## **CENICS 2015**

## Foreword

The Eighth International Conference on Advances in Circuits, Electronics and Microelectronics (CENICS 2015), held between August 23-28, 2015 in Venice, Italy, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and microelectronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics cover fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference is focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nano-electronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, eHealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements.

We take here the opportunity to warmly thank all the members of the CENICS 2015 Technical Program Committee, as well as the numerous reviewers. The creation of such a high quality conference program would not have been possible without their involvement. We also kindly thank all the authors who dedicated much of their time and efforts to contribute to CENICS 2015. We truly believe that, thanks to all these efforts, the final conference program consisted of top quality contributions.

Also, this event could not have been a reality without the support of many individuals, organizations, and sponsors. We are grateful to the members of the CENICS 2015 organizing committee for their help in handling the logistics and for their work to make this professional meeting a success.

We hope that CENICS 2015 was a successful international forum for the exchange of ideas and results between academia and industry and for the promotion of progress in the field of circuits, electronics and micro-electronics.

We hope Venice provided a pleasant environment during the conference and everyone saved some time for exploring this beautiful city.

## **CENICS 2015 Chairs:**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

## **CENICS 2015 Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

### **CENICS 2015 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

### **CENICS 2015 Publicity Chair**

Sandra Sendra Compte, Universidad Politécnica de Valencia, Spain

## **CENICS 2015 Special Area Chairs**

Formalisms Peeter Ellervee, Tallinn University of Technology, Estonia Application-oriented Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain Sensors Yulong Zhao, Xi'an Jiaotong University, China

## **CENICS 2015**

## Committee

#### **CENICS Advisory Chairs**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

#### **CENICS 2015 Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

#### **CENICS 2015 Industry Liaison Chairs**

Falk Salewski, Muenster University of Applied Sciences, Germany

#### **CENICS 2015 Publicity Chair**

Sandra Sendra Compte, Universidad Politécnica de Valencia, Spain

#### **CENICS 2015 Special Area Chairs**

#### Formalisms

Peeter Ellervee, Tallinn University of Technology, Estonia

#### **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

#### Sensors

Yulong Zhao, Xi'an Jiaotong University, China

## **CENICS 2015 Technical Program Committee**

Amr Abdel-Dayem, Laurentian University, Canada Amir Shah Abdul Aziz, TM Research & Development, Malaysia Adel Al-Jumaily, University of Technology, Sydney Said Al-Sarawi, The University of Adelaide, Australia Mohammad Amin Amiri, Iran University of Science and Technology, Iran Henri Basson, University of Lille North of France (Littoral), France Lotfi Bendaouia, ETIS-ENSEA, France Yngvar Berg, Vestfold University College, Norway Madhu Bhaskaran, RMIT University, Australia Manuel José Cabral dos Santos Reis, University of Trás-os-Montes e Alto Douro, Portugal Javier Calpe, University of Valencia, Spain James M. Conrad, University of North Carolina at Charlotte, USA Jose Carlos Meireles Monteiro Metrolho, Polytechnic Institute of Castelo Branco, Portugal David Cordeau, CNRS-XLIM, UMR 7252, University of Poitiers, France Marc Daumas, Université de Perpignan, France Javier Diaz-Carmona, Technological Institute of Celaya, Mexico Gordana Jovanovic Dolecek, Institute INAOE - Puebla, Mexico Rolf Drechsler, University of Bremen, Germany Peeter Ellervee, Tallinn University of Technology, Estonia Ykhlef Fayçal, Centre de Développement des Technologies Avancées, Algeria Sérgio Adriano Fernandes Lopes, Universidade do Minho, Portugal Francisco V. Fernández, IMSE, CSIC and University of Sevilla, Spain Joaquim Filipe, EST Setubal, Portugal Patrick Girard, LIRMM, France Luis Gomes, Universidade Nova de Lisboa, Portugal Petr Hanáček, Brno University of Technology, Czech Republic Houcine Hassan, Polytechnic University of Valencia, Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Chun-Hsi Huang, University of Connecticut, U.S.A. Wen-Jyi Hwang, National Taiwan Normal University, Taiwan Emilio Jiménez Macías, University of La Rioja, Spain Anastasia N. Kastania, Athens University of Economics and Business, Greece Kenneth Blair Kent, University of New Brunswick, Canada Eric Kerherve, University of Bordeaux, France Israel Koren, University of Massachusetts at Amherst, USA Tomas Krilavicius, Vytautas Magnus University - Kaunas & Baltic Institute of Advanced Technologies -Vilnius, Lithuania Junghee Lee, University of Texas at San Antonio, USA Kevin Lee, Murdoch University, Australia Hongen Liao, Tsinghua University, China Diego Liberati, National Research Council of Italy, Italy Alie Eldin Mady, University College Cork (UCC) - Cork, Ireland Cesare Malagu', University of Ferrara and Istituto di acustica e sensoristica Orso Maria Corbino CNR-IDASC, Italy José Carlos Metrôlho, Instituto Politécnico de Castelo Branco, Portugal Harris Michail, Cyprus University of Technology, Cyprus Yoshikazu Miyanaga, Hokkaido University, Japan Bartolomeo Montrucchio, Politecnico di Torino, Italy Adrian Muscat, University of Malta, Malta Shinobu Nagayama, Hiroshima City University, Japan Arnaldo Oliveira, Universidade de Aveiro, Portugal Adam Pawlak, Silesian University of Technology - Gliwice, Poland George Perry, University of Texas at San Antonio, USA Angkoon Phinyomark, Prince of Songkla University, Thailand Eduardo Correia Pinheiro, Instituto de Telecomunicações - Lisboa, Portugal Katalin Popovici, MathWorks, USA Adam Postula, University of Queensland, Australia Anton Satria Prabuwono, Universiti Kebangsaan Malaysia, Malaysia

Vladimir Privman, Clarkson University - Potsdam, USA Càndid Reig, University of Valencia, Spain Marcos Rodrigues, Sheffield Hallam University, U.K. Julio Sahuquillo, Universitat Politècnica de València, Spain Falk Salewski, Muenster University of Applied Sciences, Germany Marc Sevaux, Université de Bretagne-Sud, France Arvind K. Srivastava, NanoSonix Inc., USA Ephraim Suhir, University of California – Santa Cruz, USA Ivo Stachiv, National Chung-Cheng University / Institute of Physics - Czech Academy of Sciences, Taiwan / & Czech Republic João Manuel R. S. Tavares, Universidade do Porto, Portugal Felix Toran, European Space Agency, Germany Francisco Torrens, Institut Universitari de Ciencia Molecular / Universitat de Valencia, Spain Carlos M. Travieso-González, University of Las Palmas de Gran Canaria, Spain Miroslav Velev, Aries Design Automation, USA Manuela Vieira, UNINOVA/ISEL, Portugal Thomas Webster, Northeastern University, USA Chin-Long Wey, National Central University, Taiwan Robert Wille, University of Bremen, Germany Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India Sergey Y. Yurish, IFSA, Spain David Zammit-Mangion, University of Malta – Msida, Malta

## **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

## **Table of Contents**

| An Efficient Spike Detection VLSI Architecture Based on Normalized Correlator<br>Wen-Jyi Hwang, Chun-Fu Lin, and Szu-Huai Wang                                                                                          | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| COTS or Custom Made? Design Decisions for Industrial Control Systems<br>Falk Salewski                                                                                                                                   | 7  |

| Design Guidelines for Designing High Gain Patch Antenna in the Ku-band<br>Qasim Umar Khan and Mojeeb Bin Ihsan                                                                                                          | 13 |

| Filtering of Magnetic Noise Induced in Magnetometers by Motors of Micro-Rotary Aerial Vehicle Nathan Unwin and Adam Postula                                                                                             | 17 |

| Implementation and Comparison of Conventional and Ordering Based RO-PUFs for Secret Key Generation Giray Komurcu, Ali Emre Pusane, and Gunhan Dundar                                                                    | 23 |

| Hopf Bifurcation Analysis and Implementation of Single Tunnel Diode Oscillator Circuit Mustafa Fayez, Mohammad Awwad, and Hassan El-Hamouly                                                                             | 28 |

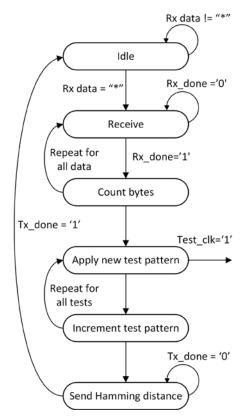

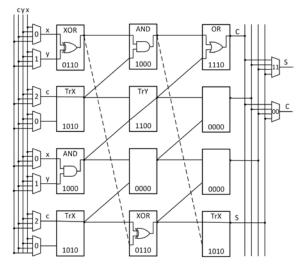

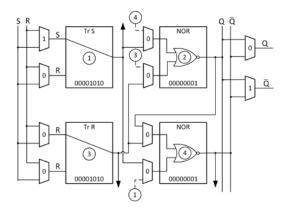

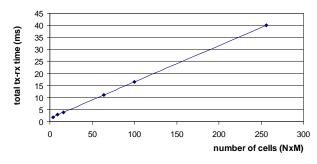

| Reconfigurable Hyper-Structures for Intrinsic Digital Circuit Evolution<br>Spyros Kazarlis, John Kalomiros, Vassilios Kalaitzis, Dimitrios Bogas, Paris Mastorokostas, Anastasios<br>Balouktsis, and Vassilios Petridis | 31 |

| Design and Implementation of a 94 GHz CMOS Down-Conversion Mixer for Image Radar Sensors<br>Yo-Sheng Lin, Chien-Chin Wang, Guo-Hao Li, and Jay-Min Liu                                                                  | 37 |

## An Efficient Spike Detection VLSI Architecture Based on Normalized Correlator

Wen-Jyi Hwang Chun-Fu Lin Szu-Huai Wang Department of Computer Science and Instrument Technology Research Center Department of Computer Science and Information Engineering National Applied Research Laboratories, Taiwan Information Engineering National Taiwan Normal University Email: vincent@itrc.narl.org.tw National Taiwan Normal University Taipei, 117, Taiwan Taipei, 117, Taiwan Email: a0919779123@gmail.com Email: whwang@csie.ntnu.edu.tw

*Abstract*—This paper aims to present an effective circuit for noisy spike detection. The circuit detects spikes by the normalized correlators. The operations of the correlators involve filtering, block energy computation, normalized correlation, and thresholding. All the computations are carried out in a pipelined fashion. The circuit has been implemented by the field programmable gate arrays (FPGAs). The circuit is used as a hardware accelerator in a network-on-chip (NOC) platform for performance evaluation. Experimental results reveal that the proposed circuit provide realtime computation for the noisy spike detection with high true postive and low false alarm rates.

Keywords-Spike Sorting; Spike Detection; FPGA; Network on Chip

#### I. INTRODUCTION

Spike sorting [1] is often desired for the design of brain machine interface (BMI) [2]. It receives spike trains from extracellular recording systems. Each spike train is a mixture of the trains from neurons near the recording electrodes. Spike sorting is able to segregate the spike trains of individual neurons from this mixture. It usually involves detection, feature extraction, and classification operations. Spike detection is the first step of the spike sorting. The goal of spike detection is to separate spikes from background noise. Extracellularly recorded signals are inevitably corrupted by noise from a number of sources such as the recording hardware and electromagnetic interference. In the presence of large noise, successful spike detection is essential for subsequent accurate feature extraction and classification.

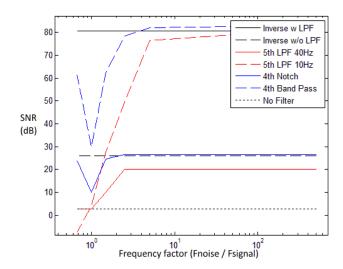

One way to perform the spike detection is based on the energy of spike trains. An example of energy-based spike detection is the nonlinear energy operator (NEO) [3], which computes the energy difference between the signal's current power and the power in adjacent time intervals. The energy of coefficients in wavelet domain may also be useful for spike detection [4]. The energy-based methods are simple and efficient. However, when noise becomes large, proper selection of threshold values for these algorithms may be difficult. Therefore, their performance may deteriorate rapidly as noise energy increases. An alternative to the energy-based methods is to utilize the templates of spikes for detection. A typical technique using templates is based on matched filters [5]. A drawback of the matched filters is the high computational complexities. Realtime spike detection may then be difficult when matched filters are implemented by software. In addition, similar to the energy-based methods, it may be difficult to find an effective threshold levels for matched filters when noise becomes large.

A number of hardware implementations for spike sorting have been proposed for reatime spike sorting. Some hardware implementations [6] are based on NEO because of is simplicity and low area costs so that the circuits may be implantable at the front end for online detection. Nevertheless, the circuits may not be suited for detection with high noise levels. In addition, hardware designs are also beneficial for offline spike sorting [8] because of the requirement for processing large amount of data. With the relaxation of implantation requirement for offline processing, development and implementation of more efficient spike detection algorithms in hardware may be desired.

The objective of this paper is to present a novel VLSI architecture for realtime spike detection for noisy spike trains. The architecture is based on normalized correlator for enhancing detection performance. Segments of spike trains are normalized prior to the correlation computation. The normalization allows the output of the correlators lie inside a range, which is independent of the input spike trains and noise levels. This is beneficial for selecting an effective threshold levels for spike detection as signal-to-noise (SNR) ratios become low.

The proposed architecture can be separated into four units: the filter unit, the block energy computation unit, the correlator unit, and the thresholding unit. All the units are operated in a pipelined fashion to enhance the throughput of the circuit. The filter unit consists of a bandpass Butterworth filter capable of removing DC and high frequency components of spike trains. The filter is helpful for noise removal prior to correlation computation and detection. The block energy computation unit is used for calculating block energy of segments of spike trains. The normalized correlation is then carried out in the correlator unit. The thresholding unit then detects spikes based on the results produced by correlator unit.

The proposed architecture can be simplified for the design of implantable circuit. By retaining only the block energy computation unit, and thresholding unit, the proposed architecture becomes an incoherent energy detector, which performs generalized likelihood ratio test (GLRT) [7] for spike detection. The incoherent energy detector has the advantages of low area costs and low power consumption, while attaining higher throughput for spike detection.

The proposed architecture has been implemented by the field programmable gate arrays (FPGAs). The circuit is employed as a hardware accelerator in a network-on-chip (NOC) platform for performance evaluation. Experimental results show that the proposed architecture is able to attain high speed detection with high true positive rate and low false alarm rate even when SNR becomes -3 dB. Its simplified

version, which performs noncoherent energy detection, has the additional advantages of lower area costs at the expense of slightly inferior detection performance. They are effective alternatives for spike sorting applications requiring real-time computation with superior spike detection performance.

The remaining parts of this paper are organized as follows. Section 2 gives a brief review of the normalized correlation algorithm. Section 3 describes the proposed spike detection architecture. Experimental results are included in Section 4. Finally, the concluding remarks are given in Section 5.

#### II. THE NORMALIZED CORRELATION ALGORITHM FOR SPIKE DETECTION

We start with the basic matched filter technique for spike sorting, which can be implemented by convolving the spike trains with the pre-stored templates. For sake of simplicity, we assume the matched filter contains only one template. Let x[n] be the *n*-th sample of the input spike train. Let  $\mathbf{x}_n = [x[n], x[n-1], ..., x[n-N+1]]^T$  be the *n*-th segment of the spike train, where N is the length of the segment. The template for matched filtering contains also N elements, denoted by  $\mathbf{t} = [t[1], ..., t[N-1]]^T$ . The matched filter output at n, denoted by, y[n], is computed from the convolution

$$y[n] = \sum_{k=0}^{N-1} x[n-k]t[k] = \mathbf{x}_n^T \mathbf{t}.$$

(1)

Note that the convolution is equivalent to the inner product of segment  $\mathbf{x}_n$  and template  $\mathbf{t}$ , which indicates the correlation between these two vectors. The segment  $\mathbf{x}_n$  is detected as a spike when y[n] is larger than a pre-specified threshold  $\eta$ .

A drawback of matched filter technique is that the threshold  $\eta$  alone cannot be used to determine the squared distance for template matching. To see this fact, we first observe that the squared distance between  $\mathbf{x}_n$  and  $\mathbf{t}$ , denoted by  $d(\mathbf{x}_n, \mathbf{t})$ , is given by

$$d(\mathbf{x}_n, \mathbf{t}) = ||\mathbf{x}_n||^2 + ||\mathbf{t}||^2 - 2\mathbf{x}_n^T \mathbf{t}.$$

(2)

Therefore, when  $\mathbf{x}_n^T \mathbf{t} > \eta$ ,

$$d(\mathbf{x}_n, \mathbf{t}) \le ||\mathbf{x}_n||^2 + ||\mathbf{t}||^2 - 2\eta.$$

(3)

Therefore, when  $\mathbf{x}_n$  is detected as a spike (i.e.,  $\mathbf{x}_n^T \mathbf{t} > \eta$ ), we see from (3) that the upper bound of  $d(\mathbf{x}_n, \mathbf{t})$  is determined from  $||\mathbf{x}_n||^2$ ,  $||\mathbf{t}||^2$  and  $\eta$ , where  $||\mathbf{x}_n||^2$  is dependent on the input spike trains. When  $||\mathbf{x}_n||^2$  is large, it is possible that  $d(\mathbf{x}_n, \mathbf{t})$  is still large even  $\mathbf{x}_n^T \mathbf{t} > \eta$ . In this case, a false alarm may occur.

One way to overcome this problem is to normalize  $\mathbf{x}_n$  and  $\mathbf{t}$  before computing the correlation. Define  $\bar{\mathbf{x}}_n$  and  $\bar{\mathbf{t}}$  as the normalized version of  $\mathbf{x}_n$  and  $\mathbf{t}$ , respectively. That is,

$$\bar{\mathbf{x}}_n = \frac{\mathbf{x}_n}{||\mathbf{x}_n||}, \quad \bar{\mathbf{t}} = \frac{\mathbf{t}}{||\mathbf{t}||}.$$

(4)

Therefore,

$$d(\bar{\mathbf{x}}_n, \bar{\mathbf{t}}) = 2 - 2\bar{\mathbf{x}}_n^T \bar{\mathbf{t}}.$$

(5)

Because  $d(\bar{\mathbf{x}}_n, \bar{\mathbf{t}}) > 0$ , it can be easily shown that

$$\bar{\mathbf{x}}_n^T \bar{\mathbf{t}} \le 1. \tag{6}$$

Our normalized correlator is based on  $\bar{\mathbf{x}}_n$  and  $\bar{\mathbf{t}}$ . When  $\bar{\mathbf{x}}_n^T \bar{\mathbf{t}} > \eta$ , then  $\mathbf{x}_n$  is detected as a spike. From (6), it follows that

$$\eta \le 1. \tag{7}$$

In addition, when  $\bar{\mathbf{x}}_n^T \bar{\mathbf{t}} > \eta$ , from (5) we see that

$$d(\bar{\mathbf{x}}_n, \bar{\mathbf{t}}) \le 2(1 - \eta),\tag{8}$$

which is dependent only on the threshold value  $\eta$ . Therefore, the threshold value for correlation computation uniquely determines the upper bound of squared distance for template matching after a spike is detected. In addition, a larger  $\eta$ implies a smaller squared distance  $d(\bar{\mathbf{x}}_n, \bar{\mathbf{t}})$ . The upper bound of  $\eta$  is 1, which is independent on the input spike trains.

The normalized correlator has more meaningful interpretation for the threshold value  $\eta$  because  $\eta \leq 1$ , and the upper bound of squared distance for template matching for a detected spike is  $2(1-\eta)$ . When  $\eta = 1.0$  is selected for detection, only the segments having *full* correlation with the template t are considered as spikes, and their squared distance with t is 0. When  $\eta = 0.5$ , all the segments having *half* correlation (or above) with t are detected as spikes, and the upper bound of their squared distances is 1. When  $\eta = 0$ , even the segments having no correlation with t are detected as the spikes, and the upper bound of their squared distances increases to 2. In the presence of noise, it may be impractical to require the detected spikes as the segments having full correlation (i.e.,  $\eta = 1.0$ ). In our experiments, the requirement of 70 % correlation (i.e.,  $\eta = 0.7$ ) may be sufficient for the normalized correlator to attain high detection hit rate, low miss rate, and low false alarm rate even for high noise levels. Detalied discussions of the normalized correlator can be found in our earlier work in [9].

Although the normalized correlator simply the process for the selection of threshold values, it has higher computation complexities for spike detection as compared with the basic matched filter technique. This is because the block energy of each segment need to be computed prior to the correlation computation. Hardware implementation of the normalized correlator may be beneficial for enhancing the throughput of the normalized correlator for realtime spike sorting.

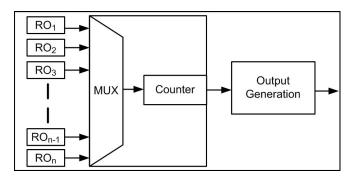

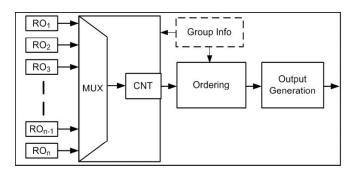

#### III. THE PROPOSED ARCHITECTURE

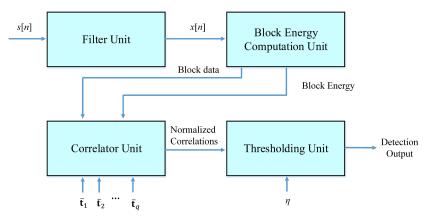

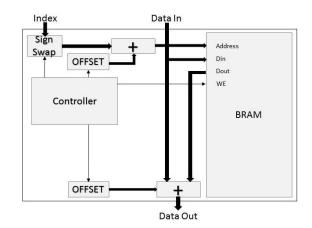

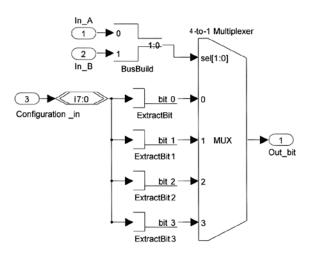

Figure 1 shows the block diagram of the proposed architecture, which contains the filter unit, and block energy computation unit, the correlator unit, and thresholding unit. The filter unit is the pre-processing unit for the spike detection. It removes both the DC offset and noises before the detection operation. The goal of the block energy computation unit is to compute the block energy  $||\mathbf{x}_n||^2$ . The correlator unit then calculates  $\bar{\mathbf{x}}_n^T \bar{\mathbf{t}}$ . The detection results are then produced by the thresholding unit.

#### A. Filter Unit and Block Energy Computation Unit

In the implementation, the bandpass butterworth filter is used for the preprocessing operations. The filter can be implemented by shift registers, multipliers and adders. For sake of simplicity, the details of the implementation is not included. The direct implementation of the block energy computation involving N multiplications is also straightforward. Although N multipliers can be employed for the multiplications, the area

Figure 1. The Block Diagram of the Proposed Architecture for q templates

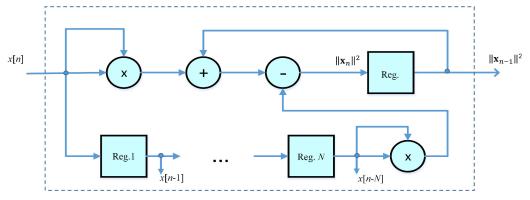

Figure 2. The Architecture of the Block Energy Computation Unit

costs can be high. An alternative is based on the observation that

$$|\mathbf{x}_n||^2 = ||\mathbf{x}_{n-1}||^2 + x^2[n] - x^2[n-N].$$

(9)

Therefore, when the block energy of the previous block (i.e.,  $||\mathbf{x}_{n-1}||^2$ ) is known, the computation of the block energy of the current block needs only two multiplication for the computation of the square of the samples x[n] and x[n-N], as shown in Figure 2. There are one N-stage shift register, two multiplier and two adders in the block energy computation unit. The shift register is used to hold the values of the past samples (i.e., x[k], k = n-1, ..., n-N) in the first-in-first-out (FIFO) fashion. In addition to providing the value x[n-N] for the computation of  $x^2[n-N]$ , the shift register is beneficial for the correlation computation in the correlator unit.

#### B. Correlator Unit

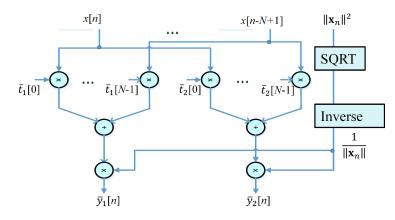

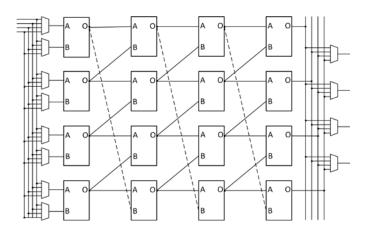

In addition to multiplications, the correlator for the computation of  $\bar{y}[n] = \bar{\mathbf{x}}_n^T \bar{\mathbf{t}}$  requires the normalization operations. Although the normalized template  $\bar{\mathbf{t}}$  can be obtained offline, the computation of the normalized  $\bar{\mathbf{x}}_n$  should be carried out online. A direct implementation of the circuit for the computation of  $\bar{\mathbf{x}}_n$  is to divide each sample of  $\mathbf{x}_n$  by  $||\mathbf{x}_n||$ . This would require N dividers, because the dimension of the block  $\mathbf{x}_n$  is N. An alternative is based on the post-normalization technique, in which the inner product  $\mathbf{x}_n^T \bar{\mathbf{t}}$  is computed first. Because the inner product is a scalar, we can then use only one divider to compute  $\bar{\mathbf{x}}_n^T \bar{\mathbf{t}}$  by dividing  $\mathbf{x}_n^T \bar{\mathbf{t}}$  by  $||\mathbf{x}_n||$ . Figure 3 shows the architecture of the correlator unit for the case of two templates. Correlators for any q > 0 templates can be carried out in a similar fashion. As shown in the figure, there are 2N multipliers, two accumulators, one squared root circuit, and one divider. The samples of  $\mathbf{x}_n$  are obtained from the shift register in the block energy computation unit. The normalized templates  $\bar{\mathbf{t}}_1$  and  $\bar{\mathbf{t}}_2$  are pre-stored in the registers of the unit. To accelerate the correlation computation, there are N multipliers for the computation of each  $\bar{\mathbf{x}}_n^T \bar{\mathbf{t}}_i$ , i = 1, 2. In addition, the accumulation of the multication results are carried out in a pipelined fashion. The output of each accumulator is then divided by by  $||\mathbf{x}_n||$ . Observe from Figure 2 that the output of the block energy computation unit is  $||\mathbf{x}_n||^2$ . Therefore, the squared root (SQRT) circuit can be used to compute  $||\mathbf{x}_n||$ , as shown in Figure 3.

#### C. Thresholding Unit

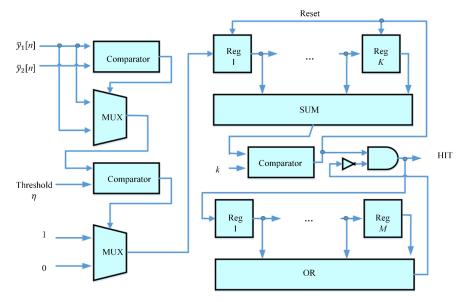

Although the thresholding operations can be easily accomplished by a simple comparison circuit, the detection accurracy may be further improved by taking the detection results of the neighboring blocks into consideration. Because the neighboring blocks are overlapping, it is then likely that these blocks have similar normalized correlation values. A number of neighboring blocks may then have normalized correlation values larger than a pre-specified threshold. Consequently, it is possible that multiple hits may be declared for the occurrence of a single spike.

One way to solve this problem is not to declare a hit

Figure 3. The Architecture of the Correlator Unit for q = 2 Templates

Figure 4. The Architecture of the Thresholding Unit for q = 2 templates

when the normalized correlation value of a block is above the threshold. The normalized correlation values of the previous blocks are also ckecked. Among its K preceding blocks, if k of them are also above the threshold, a hit is then declared. This may effectively reduce the false alarm rate for the detection. The architecture of the thresholding unit is revealed in Figure 4. It can be observed from the figure that a K-stage shift register is used to store the thresholding results of the K previous blocks. Each stage contains 1-bit information, where 0 and 1 indicate the corresponding block has correlation value below and above the threshold  $\eta$ , respectively. Consequently, when the sum of the output of all the K stages is equal or above k, then k of the K preceding blocks have correlation value above the threshold. A hit is then issued.

Note that we may be able to further reduce the false alarm rate at the expense of a slight increase in true positive rate by imposing the assumption that spikes are at least M samples apart. The enforcement of the assumption can be carried out be an additional M-stage shift register recording the location of the previous hit. Each stage also has values of 0 or 1. If the previous hit is less than M samples apart, one of the stage in the shift register contains value of 1, which disables the hit. A hit is allowed to be issued only when all the stages contain value of 0.

#### D. Noncoherent Energy Detector

The proposed circuit can be simplified by removing the correlator unit. In this case, the output  $||\mathbf{x}_n||^2$  of the block energy computation unit is connected directly to the thresholling unit. The circuit will declare a hit when  $||\mathbf{x}_n||^2$  is above the threshold. This is the noncoherent energy detector proposed by [7]. As compared with the proposed circuit, the noncoherent energy detector has the advantages of lower area costs and power consumption at the expense of slightly lower true positive rates and/or higher false alarm rates. The circuit is advantageous for the applications where both the speed and area costs are the important concerns.

#### IV. EXPERIMENTAL RESULTS

This section presents some experimental results of the proposed architecture. The simulator developed in [10] is

| SNR (dB) |     | Normalized Noncoherent |                 | NEO     | SWT     | Matched |

|----------|-----|------------------------|-----------------|---------|---------|---------|

|          |     | Correlator             | Energy Detector |         |         | Filter  |

| 10       | TPR | 93.64 %                | 91.37 %         | 93.10 % | 94.82%  | 89.65 % |

|          | FAR | 0.40 %                 | 5.35 %          | 3.57 %  | 6.77 %  | 2.80 %  |

| 1        | TPR | 90.04 %                | 88.03 %         | 87.21 % | 92.43 % | 82.90 % |

|          | FAR | 0.92 %                 | 6.36 %          | 22.49 % | 79.36 % | 3.02 %  |

| -3       | TPR | 82.71 %                | 82.60 %         | 80.53 % | 86.66 % | 80.31 % |

|          | FAR | 1.06 %                 | 9.52 %          | 57.87 % | 82.43 % | 8.92 %  |

TABLE I. THE TPR AND FAR VALUES OF VARIOUS SPIKE DETECTION ALGORITHMS FOR SPIKE TRAINS WITH VARIOUS SNR LEVELS.

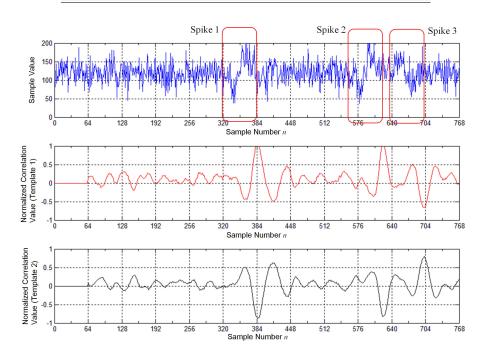

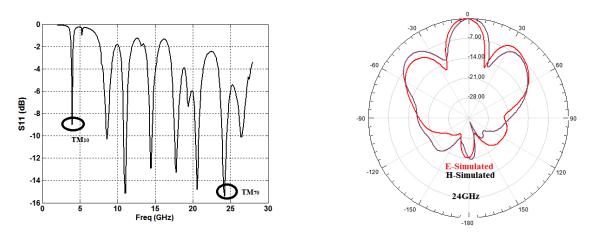

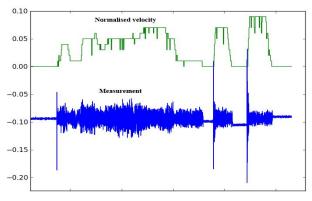

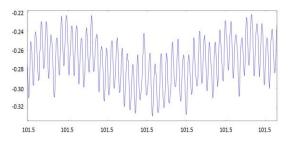

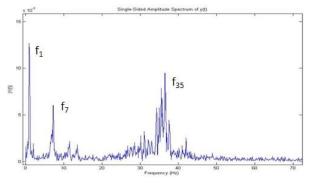

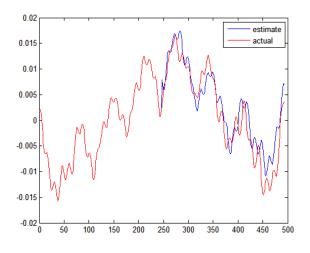

Figure 5. An example of the proposed normalized correlator for noisy spike detection with SNR=-3 dB for q = 2 templates.

adopted to generate extracellular recordings. The simulation gives access to ground truth about spiking activity in the recording. This facilitates the quantitative assessment of the proposed architecture, since the features of the spike trains are known a priori. All the spikes are recorded with a sampling rate of 24,000 samples/s. Each spike has 64 samples (i.e., N = 64), and the length of each spike is 2.67 ms.

We first consider the true positive rate (TPR) and false alarm rate (FAR) of the proposed architecture. The TPR is defined as the number of detected true spikes divided by the total number of true spikes. The FAR is defined as the number of silent segments, which are detected as spikes, divided by the total number of detected segments. Table I shows the TPR and FAR of the normalized correlator, the noncoherent energy detector, NEO, stationary wavelet transform (SWT), and matched filter for various SNR levels. The number of neurons is 2. The proposed normalized correlator architecture therefore uses 2 templates (i.e., q = 2).

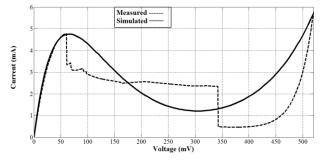

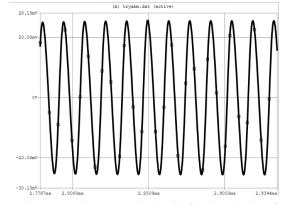

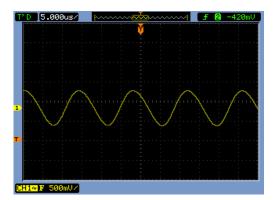

It can be observed from Table I that the normalized correlator has higher TPR and lower FAR as compared with those of the other algorithms. This is because the correlation is beneficial for identifying real spikes and ignoring silent segments. This fact can be further observed in Figure 5, where the noisy spike train with SNR= -3 dB, and the normalized correlation values  $\bar{y}_i[n], i = 1, 2$ , are shown. It can be observed from Figure 5 that it is difficult to locate spikes due to large noise corruption. Nevertheless, the normalized correlation values shown in Figures 5 still provide useful information revealing the location of true spikes. It is also interesting to note that the noncoherent energy detector has TPR and FAR values comparable to those of matched filter. These results show that the energy is also effective for spike detection.

Next we evaluate the area complexities. Because adders, multipliers, dividers, comparators and registers are the basic building blocks of the architecture, the area complexities are separated into four categories: the number of adders, multipliers, dividers, comparators and registers. Table II shows the area complexities of the proposed architecture. It can be observed from Table I that the number of adders, multipliers, and dividers are fixed, and independent of the block dimension N and number of templates q in the filter unit, block energy computation unit and thresholding unit. Although the number of adders and the number of multipliers grows with the N and

TABLE II. THE AREA COMPLEXITIES OF THE PROPOSED ARCHITECTURE

|             | Filter | Block Energy     | Correlator | Thresholding |

|-------------|--------|------------------|------------|--------------|

|             | Unit   | Computation Unit | Unit       | Unit         |

| Adders      | O(1)   | O(1)             | O(qN)      | O(1)         |

| Multipliers | O(1)   | O(1)             | O(qN)      | O(1)         |

| Dividers    | 0      | 0                | O(1)       | 0            |

| Comparators | 0      | 0                | 0          | O(1)         |

| Registers   | O(1)   | O(N)             | O(qN)      | O(1)         |

TABLE III. HARDWARE UTILIZATION OF THE FPGA IMPLEMENTATION OF THE PROPOSED NORMALIZED CORRELATOR ARCHITECTURE

|             | Filter | Block Energy     | Correlator | Thresholding | Total |

|-------------|--------|------------------|------------|--------------|-------|

|             | Unit   | Computation Unit | Unit       | Unit         |       |

| ALUTs       | 750    | 649              | 4571       | 89           | 6059  |

| Registers   | 236    | 866              | 2788       | 13           | 3903  |

| Memory Bits | 0      | 0                | 0          | 0            | 0     |

| DSP Blocks  | 24     | 3                | 528        | 0            | 555   |

q in the block energy computation unit, only a single divider is used in the unit because of the employment of the postnormalization technique. This is beneficial for lowering the area costs of the circuit.

We further consider the hardware utilization of the proposed normalized correlation architecture implemented by FPGA. In the experiments, we set the dimension of the spikes to be N = 64. There are q = 2 templates. The target FPGA in the experiments is Altera Stratix III EP3SE80F780C2, which contains 64,000 adaptive lookup tables (ALUTs), 64,000 registers, 6,331,392 memory bits, and 672 DSP blocks. The FPGA design platform is Altera Quartus II 13.0. Table III shows the number of ALUTs, the number of registers, the number of memory bits, and the number of DSP blocks consumed by each unit of the proposed circuit. It can be observed from Table III that many of the ALUTs, registers and DSP blocks provided by the target FPGA are consumed by the correlator unit because the inner product operations are required in the unit.

When only the noncoherent energy detection is necessary, the correlator can be removed. Therefore, the area costs can be effectively lowered. Table IV shows the hardware utilization of the proposed normalized correlation architecture and the proposed noncoherent energy detection architectures. It can be observed from Table IV that the noncoherent energy detection architecture has lower hardware utilization. In particular, the utilization of DSP blocks is 3, which is only 0.54 % (i.e., 3/555) of that utilized by the normalized correlator architecture.

The proposed architecture is used as a hardware accelerator in a NOC platform for the speed evaluation. The NOC is designed by Altera Qsys 13.1. The NOC consists of a NIOS II softcore processor, an embedded RAM, and the proposed circuit. The noisy spike sequences are stored in the embedded RAM. The NIOS II processor activates the delivery of the spike sequence from the RAM to the proposed circuit for spike detection. Upon the completion of spike detection operations, it also collects the results of the spike detection for subsequent spike sorting operations. When operating at the clock rate 50 MHz, the proposed architecture is able to complete the

TABLE IV. COMPARISONS OF HARDWARE UTILIZATION OF THE NORMALIZED CORRELATOR AND NONCOHERENT ENERGY DETECTOR FPGA IMPLEMENTATIONS

|                 | ALUTs | Registers | Memory Bits | DSP Blocks |

|-----------------|-------|-----------|-------------|------------|

| Normalized      |       |           |             |            |

| Correlator      | 6059  | 3903      | 0           | 555        |

| Noncoherent     |       |           |             |            |

| Energy Detector | 1488  | 1115      | 0           | 3          |

detection operation in 52 ms for a spike sequence with length of 100 seconds. By contrast, the computation time of its software counterpart running in the 1.7 GHz Intel I-7 processor for the same spike sequence is 1.58 second. The speedup of the hardware acceleration therefore in 30.38 (i.e., 1.58 second vs. 52 ms). All these facts demonstrate the effectiveness of the proposed architecture.

#### V. CONCLUSION

The proposed normalized correlator architecture has been implemented by FPGA for performance evaluation. Experimental results show that the architecture is effective for spike detection. It has the advantages of high TPR, low FAR, and fast computation. For spike trains with SNR = -3 dB, the proposed normalized correlator is able to achieve TPR 82.71 % and FAR 1.06 %. In addition, the speedup of the proposed architecture in the NOC operating at 50 MHz over its counterpart is 30.38. The proposed architecture can also be simplified to a noncoherent energy detector when lower hardware costs are desired at the expense of a slight degradation in detection performance.

#### REFERENCES

- [1] S. Gibson, J. W. Judy, and D. Markovic, "Spike sorting: the first step in decoding the brain," IEEE Signal Processing Magazine, 2012, pp. 124-143.

- [2] M. A. Lebedev and M. A. L. Nicolelis, "Brainmachine interfaces: past, present and future," Trends in Neurosciences, Vol. 29, 2006, pp. 536-546.

- [3] S. Mukhopadhyay and G. C. Ray, "A new interpretation of nonlinear energy operator and its efficacy in spike detection," IEEE Trans. Biomed. Eng., Vol. 45, 1998, pp. 180-187.

- [4] K. Kim and S. Kim, "A wavelet-based method for action potential detection from extracellular neural signal recording with low signal-tonoise ratio," IEEE Trans. Biomed. Eng., Vol. 50, 2003, pp. 999-1011.

- [5] N. Mtetwa and L. S. Smith, "Smoothing and thresholding in neuronal spike detection," Neurocomputing, Vol. 69, 2006, pp. 1366-1370.

- [6] J. Drolet, H. Semmaoui, and M. Sawan, "Low-power energy-Based CMOS digital detector for neural recording arrays," IEEE Biomedical circuits and systems conference, 2011, pp.13-16.

- [7] K. Oweiss and M. Aghagolzadeh, Detection and classification of extracellular action potential recordings, Chapter 2 of Statistical Signal Processing for Neuroscience, 2010, pp. 15-74.

- [8] S. Gibson, J. W. Judy, and D. Markovic, "An FPGA-based platform for accelerated offline spike sorting," Journal of Neuroscience Methods, Vol. 215, 2013, pp. 1-11.

- [9] W. J. Hwang, S. H. Wang, and Y. T. Hsu, "Spike Detection Based on Normalized Correlation with Automatic Template Generation," Sensors, 2014, pp. 11049-11069.

- [10] L. S. Smith and N. Mtetwa, "A tool for synthesizing spike trains with realistic interference," Journal of Neuroscience Methods, Vol. 159, 2007, pp. 170-180.

## **COTS or Custom Made? Design Decisions for Industrial Control Systems**

Falk Salewski

Department of Electrical Engineering and Computer Science Muenster University of Applied Sciences Germany

Email: falk.salewski@fh-muenster.de

*Abstract*—In the area of industrial control systems, the choice between *custom made* (CM) electronics and the use of *commercial* of the shelf (COTS) components is often not trivial. Especially, when required quantities or specific requirements do not give a clear sign for selection. From a pure cost point of view (development costs and product costs) a decision might look trivial, but a broader view helps to perform an sound decision. In this work, decision criteria and a decision method are presented for industrial control systems targeting COTS devices, CM devices or a combination of both. Moreover, a case study with three industrial control systems is presented showing the application of the approach.

Keywords-commercial of the shelf; electronic design decisions; industrial control units

#### I. INTRODUCTION

In industrial automation, commercial of the shelf (COTS) components as programmable logic controllers (PLCs) and industrial PCs (IPCs) are widely used as control units (For this paper, we follow the following definition for COTS: A COTS device can be bought from a catalog without modifications [1]). In some applications, companies are faced with the decision if a custom made (CM) design of a control unit might be beneficial for their products and systems. In other application, a change from a custom made design of control units to COTS components is discussed.

A custom made development often comes with an optimized functionality and an attractive price of the final product, but involves much more than own development activities. Especially in case of safety or mission critical systems, it has to be assured that specific requirements (temperature range, failure rate, electrical robustness, etc.) are met over the complete product life cycle (and not only with a prototype during development). While a custom made design allows full control of the final product, all relevant aspects have to be verified. These activities are performed on basis of prototypes and first series devices, but also have to be reconsidered in case of changes (e.g., obsolete memory chips require replacement).

On the other hand, the use of COTS components often requires more than applying a plug and play procedure. In the example of COTS components in critical applications, it could be required to establish specific relationships with the suppliers and/or to perform additional tests on the COTS components (examples can be found in [1]).

In both cases, the complete life cycle of the product has to be considered for a sound selection. An approach for such a selection is the so called Total Cost of Ownership (TCO) [2] that aims to consider all cost factors of a product during product life. To supplement existing approaches with the required technical data, this paper deals with the differences of the following approaches for industrial control units:

- 1) Commercial of the shelf (COTS)

- 2) Custom made (CM)

- 3) Combination of 1 and 2.

The main focus of this paper is on electronic control units (including their software), but not on pure software products as discussed for example in [3].

As a basis for a systematic selection procedure, we collect relevant selection criteria in the following Section II. Next, the specialties of the three approaches are analyzed based on their product life cycle in Section III. Based on these two sections, a selection procedure is presented in Section IV, followed by a case study in Section V. After a discussion in Section VI, the paper ends with a conclusion.

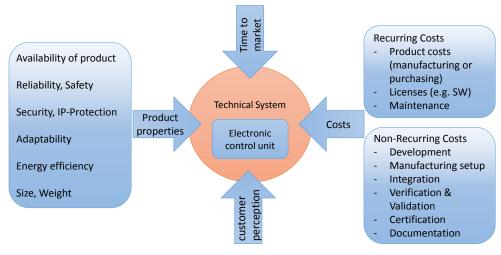

#### II. TARGETS FOR SELECTION

Before having a closer look on the different approaches, it is necessary to define the key targets to be fulfilled by the devices. Common targets often cited are fast time to market, improved costs and competitive advantages [4]. These competitive advantages describe product properties beside the price and differ between application domains. In previous work, we already identified a set of impact factors for hardware platforms [5]. For this work, we take a system view on the control units (electronics + software + mechanical). Moreover, we assume that the functional requirements are fulfilled for industrial environments in case of all candidates. The resulting set of impacts is presented in Figure 1 and will be further described below.

#### A. Time to Market

A fast *time to market* is an obvious target. As soon as the product is on the market amortization of non-recurrent costs can start. Moreover, a fast *time to market* can be a competitive advantage to competitors.

#### B. Costs

As with *time to market*, it is an obvious target to keep the *costs* low. However, several aspects have an impact on the overall costs for a product. In case of *recurrent costs*, it is the cost of purchasing or manufacturing the product itself. In addition, license costs for software (drivers, operating systems, etc.) and/or hardware modules (e.g., inclusion of externally developed modules in custom made products) as well as

Figure 1. Targets for selection of electronic control units

costs resulting from later maintenance activities have to be considered. The non-recurrent costs for a custom made control unit include development costs (including costs for prototypes and test activities during development) as well as costs for the preparation of the series production (creation and test of tooling, as soldering frames, adapters for automatic assembly, programs for test equipment as automated optical inspection (AOI), in circuit tester (ICT), and/or functional tester, test adapters and specific test electronics). Further non-recurrent costs that also appear for COTS systems are the costs of integration of the electronic control system into the target system as well as those for verification, validation and certification activities (performed before and/or after integration in target system). Often, at least certification activities are executed on system level, but benefit from pre-certified components. Finally, costs resulting from required documentation activities (product + development process) have to be considered.

#### C. Product Properties

While we assume that all candidates can fulfill the functional requirements, further properties could make a difference.

A first important property is the *availability* of the product (availability in this context is not the operational availability but the possibility to purchase or manufacture the product). For any application, it is important that the required control electronics are available for new products and replacements of defect units.

As many industrial control electronics perform safety and/or mission critical tasks, their *reliability* and *functional safety* is another important factor. As evaluated in previous work, the choice of the hardware platform has impacts on the safety properties of the overall system [6]. The specific needs have to be analyzed for each application individually.

Security is another important property. Especially the increasing interconnection of industrial automation systems via the internet requires corresponding measures [7], [8], [9]. Additionally, a protection of the *intellectual property* (IP: firmware, electronics, design, etc.) is often desirable to protect own products from plagiarizing. As with functional safety and reliability, the requirements depend on the individual application.

For applications that evolve during their life time (e.g., an industrial plant undergoing modernization) or those in which a control unit should be applied in several different target applications (perhaps not all of them defined today), it is desirable to work with systems that can be *adapted* to different or changing requirements. Examples are modular PLCs which allow to add a variety of different plug-in modules (analog and digital I/O, communication interfaces, special function modules). Another approach is to define major parts of the product via software or reconfigurable hardware (e.g., FPGAs).

While *energy efficiency* of control units was predominantly an issue in mobile and battery powered devices in the past, it is now also an issue in all industrial application (especially if a high number of control units is applied). Additionally, *size* and/or *weight* is an issue in several applications.

#### D. Customer Perception

Finally, an impact that could be important is the customer perception. While a decision could not be the optimum choice, it still might be the optimum solution from the customers perspective. As an example, the use of a COTS device with a good reputation might increase customer's confidence in the product although it does not differ from alternatives from a technical point of view.

#### III. PRODUCT LIFE CYCLE

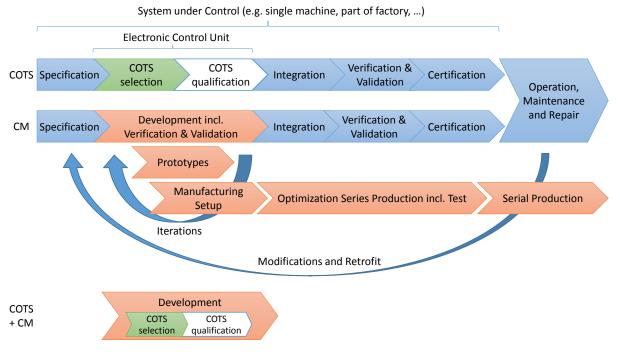

In this section, a typical product life cycle is presented in Figure 2 for a design based on COTS control units, a design with custom made control units and a combination of COTS and CM components.

Following accepted processes, the product life cycle starts with a specification. While the creation of a sound specification is a major task, we assume it is already existent for the next step. Based on the specification, an implementation could be realized in the three ways presented above. Additionally, each product life cycle ends with some *end of life* activities, typically decommissioning. As the impact of this phase is considered low for the selection process, end of life activities are not considered in this paper. The following subsections deal with the remaining phases for the three approaches.

Figure 2. Product life cycle for different approaches (length of phases does not necessarily reflect the effort required for this phase)

#### A. COTS

In case of a COTS design, a suitable device has to be selected. The aim is to identify an existing product that fulfills the requirements given in the specification. Moreover, further aspects as those presented above could be important for the selection, although often not explicitly stated in the specification. Depending on the application, it might be useful to reconsider the specification, if no suitable COTS device could be identified. Moreover, the fulfillment of the requirements is often not only determined by the product itself and related aspects (e.g., documentation), but also by the relationship to the supplier of this device (support during integration, operation, maintenance, long time availability, insight into verification and validation activities, willingness to perform further verification and validation activities if needed, etc.). Especially for critical applications, additional verification activities could be required to apply COTS devices (see [1] as an example for military applications). If these verification activities are required and cannot be performed by the supplier, own verification activities have to be performed with the COTS device.

In the next phase, the selected COTS device has to be integrated into the application (for this approach, we assume that no modifications are required to integrate the COTS device). In this phase, the knowledge of the COTS device's properties is of great importance. Gaining this knowledge could be time consuming, but could be eased by support given by the supplier (good documentation, qualified hotline support, tools supporting integration, etc.).

While verification and validation of the control unit itself has already been targeted, it is the overall system that has to fulfill the requirements. Thus, verification and validation activities have to be performed also on system level. Based on the application, also certifications are required or recommended (e.g., functional safety applications). Several COTS devices come with some pre-certification for certain applications (as the mentioned safety applications). These pre-certifications typically ease the certification activities on system level.

#### B. Custom Made

The CM approach requires development and manufacturing activities. During development, prototypes are implemented and verified on basis of the specification. Design decisions have to consider functional aspects, as well as further impacts (see Figure 1). Some aspects for COTS apply here for specific integrated circuits used in the design. They can simplify design and verification activities, but also lead to the challenges listed in the COTS section (e.g., availability). Especially in complex designs, often several prototype stages are required until verification and validation activities are passed successfully. Additionally, an ideal design is optimized for later manufacturing reducing manufacturing times and tooling costs. Generally speaking, the aim is to deal with the complexity in development and manufacturing [10]. For optimum timeto-market, the preparation for manufacturing is started before the development activities are finished. The required synchronization between development and manufacturing activities are often challenging [11]. Moreover, to determine the start time of preparation activities, a tradeoff between risks of changes in the product relevant for production and reduced preparation time is necessary.

In the following steps, optimizations of the manufacturing process take place, mostly to optimize manufacturing time and quality. Integration, verification and validation activities can start with prototypes, but final tests and certification typically require first samples from the serial manufacturing process.

In case of a COTS product, analysis of defect products, obsolete components or changes in regulatory requirements (e.g., EMC requirements) are typically performed by the supplier. Also in case of a CM design, this analysis has to be performed periodically to check if changes in the product are required. While these activities could be outsourced, the effort for these activities has to be considered. Moreover, required changes could result in costly redesign activities (new verification, validation and certification activities might be needed), a risk worn by the supplier in case of COTS components.

#### C. Combination

The process of combining COTS components with a custom made design follows a combination of both processes. Typically, the product core is implemented with a COTS component and the interfaces are custom made, but also other parts as interfaces or power supplies can be implemented with COTS parts. Thus, during development all aspect of a custom made design have to be followed in addition to a selection of suitable COTS components (lower part of Figure 2, only the differences to the CM process are displayed). While the use of COTS components comes with some challenges to be considered (see section above), it can simplify the remaining development significantly. An example is the use of a COTS single board PC on a custom made printed circuit board (PCB) populated with interface and power supply circuits (and some application specific functions if needed, see also Section V). This combination can simplify the manufacturing process if the main PCB is populated with comparatively simple components only. Furthermore, PC parts tend to become easily obsolete, a problem now covered by the supplier of the PC board. But the supplier of the PC board benefits from his high production volume. Thus, the resulting price of the PC module could be lower than to manufacture low quantities in house.

#### IV. SELECTION PROCEDURE

Based on the targets presented in Section II and the product life cycles presented in the preceding Section III, a systematic selection is feasible. For an objective evaluation, it is recommended to evaluate each factor in a team (at least technical and sales representatives). In case a custom made design might be the desired choice, experts from the area of electronic development and manufacturing should be consulted (internal or external partners). This way, quantitative data can be achieved for costs and time-to-market aspects. However, for reliable data, a sound specification and "trustworthy" experts are required.

Besides costs and time to market, the targets are of qualitative nature. While a qualitative analysis is probably sufficient in many cases, a rating system can be applied in case of all qualitative aspects (e.g., rating of products availability from 1 to 10) if needed, for example in form of a decision matrix. Rating can be agreed on in the team or it can be build from a set of individual ratings. Further approaches for these so called *multi-criteria decision analysis* (MCDA) can be found in literature (e.g., [12]).

#### V. CASE STUDY

In this section, three existing control units are evaluated based on the criteria defined before. The emphasis of the following description is on the properties of the selected system and not on the selection process (devices already exist).

#### A. Three Control Units

1. Machine for sorting metal parts: The control unit is required to switch electric motors and pneumatic valves and read several position sensors and an analogue input for measuring the metal parts. Moreover, the status of the machine has to be displayed on a screen. The volume of this machine is  $\leq 50$ per year.

2. User terminal for embroidery machine: The Control unit has to read the required embroidery pattern from a USB stick and display it on the screen of the terminal. Moreover, user commands have to be read from the terminal. A set of commands is computed and send to the embroidery machine via a proprietary interface. The volume is 800 units per year.

3. Window control unit: This electronic unit has to control a DC motor (PWM, encoders) based on sensor information and a proprietary bus interface. Moreover, the available space for this device is limited to 100x40x18mm. The volume here is  $\geq 1000$  units per year.

#### B. Evaluation

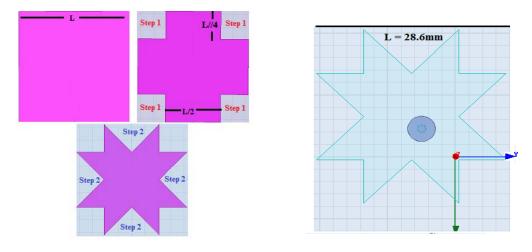

An overview of the evaluation can be found in Figure 3 while details will be described below.

1) Case A: The low quantity of required products indicate a COTS device as best choice. However, a conflict could arise from the remaining targets. The non recurrent costs, as well as the required time to market clearly benefit from the use of a COTS component. The recurrent price is probably higher than a custom made approach, but a quantity of 50 units in most cases does not allow to amortize non recurrent costs for a custom made design incl. verification. Finally, product properties have to be considered. Size and Weight targets, as well as energy efficiency, which could be a tough challenge for COTS approaches, are not critical here. For this application, a modular programmable logic controller (PLC) has been chosen. This approach allows to adapt the control units in case of later changes. Moreover, this approach allows to use similar approaches in different machines. During the selection of the device, the availability of this device or potential replacements is crucial. Well established systems, as well as individual contracts can mitigate the risks. Additionally, the use of standardized components (including the programming languages) ease the migration to alternative systems when needed. Finally, no specific safety, security or reliability requirements were given in this application. However, specific PLC systems targeting these requirements are available. Based on this brief evaluation, a COTS approach is the optimum solution for this application.

2) Case B: In this application, the need for a proprietary interface requires at least some custom made design. Moreover, the visualization requirements for the terminal screen require a certain amount of processing power. In this application, a combination of a COTS processor board was chosen in combination with a custom made main board implementing the power supply and required interfaces. The use of the COTS board was driven by the following aspects:

- simplifies design and manufacturing of main board (no fine pitch components, less high speed design)

- in required quantities, COTS board has an attractive price compared to CM approach.

|                   | Case :                              | Case A                                                                                                                                                                           | Case B                                                                                                                                                                                                                 | Case C                                                                                                                                                         |  |

|-------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   | Description :                       | Machine for sorting metal parts                                                                                                                                                  | User terminal for embroidery machine                                                                                                                                                                                   | Window control unit                                                                                                                                            |  |

| Assum             | ned annual quantity :               | ≤ 50                                                                                                                                                                             | 800                                                                                                                                                                                                                    | ≥ 1000                                                                                                                                                         |  |

| Target            | s $\downarrow$ Choice $\rightarrow$ | COTS                                                                                                                                                                             | COTS + CM                                                                                                                                                                                                              | СМ                                                                                                                                                             |  |

| Product           |                                     | high, but according to low quantity best<br>with COTS device (here PLC)                                                                                                          | combination of a COTS processor board<br>with a custom made main board allows a<br>competitive product price                                                                                                           | custom made design allows cost optimized approach (for given constraints)                                                                                      |  |

| Recurring         | Licenses                            | no licence for operation                                                                                                                                                         | open source operating system                                                                                                                                                                                           | none                                                                                                                                                           |  |

| Recurring         | Maintenance                         | diagnosis features supported by PLC,<br>modular PLC allows replacement/ repair of<br>modules                                                                                     | individual repair/replacement of processor<br>and main board possible, maintenance<br>features have to be custom made                                                                                                  | diagnosis features implemented via bus<br>interface                                                                                                            |  |

|                   | Development                         | HW: only selection & integration<br>SW: based on PLC operating system =><br>application only                                                                                     | HW: only main board + selection processor<br>board & integration<br>SW: operating system has to be adapted to<br>custom design + application SW                                                                        | full development of electronics and software                                                                                                                   |  |

| Costs             | Manufacturing<br>Setup              | none                                                                                                                                                                             | manufacturing of main board + integration<br>processor board + test in manufacturing;<br>separate processor board, no fine pitch<br>devices on main board => simplifies<br>manufacturing process                       | full manufacturing setup incl. test required                                                                                                                   |  |

| Non-<br>Recurring | Integration                         | HW setup with COTS IDE + wiring of sensors and actuators                                                                                                                         | <ol> <li>main and processor board</li> <li>operating system and HW</li> <li>application</li> </ol>                                                                                                                     | HW/SW integration in development,<br>integration with remaining system via bus<br>interface                                                                    |  |

|                   | V&V                                 | focus on SW + overall system                                                                                                                                                     | complete system                                                                                                                                                                                                        | complete system                                                                                                                                                |  |

|                   | Certification                       | not required for control unit                                                                                                                                                    | EMC test for CE marking                                                                                                                                                                                                | EMC test for CE marking,<br>further tests with complete system                                                                                                 |  |

|                   | Documentation                       | SW + wiring (hardware configuration saved<br>in project data)                                                                                                                    | full documentation,<br>exisiting documentation for processor board<br>and operating system can be included                                                                                                             | full documentation                                                                                                                                             |  |

|                   | -                                   | depends on PLC supplier, long term<br>industrial availability provided                                                                                                           | depends on supplier of processor board<br>(long term contract), processor board can<br>be replaced (redesign main board +<br>comparable alternative processor board)                                                   | depends only on components used,<br>obsolences can be handeld with 2nd source<br>components, if needed in combination with<br>redesign (HW or HW+SW)           |  |

|                   |                                     | no specific requirements, COTS HW is<br>assumed to be well tested,<br>COTS devices typically = black box, but<br>reliability and safety data is available for<br>certain devices | complete reliability analysis possible for<br>main board, data für processor board<br>available from supplier.<br>No specific safety requirements.<br>(implementation on main board could be an<br>option if required) | complete reliability analysis possible for<br>electronics.<br>Specific safety requirements could be<br>implemented in SW and HW (emergency<br>stop, life beat) |  |

| Product           | Security & IP-<br>Protection        | supported, setting via COTS IDE                                                                                                                                                  | processor supports protection of program<br>memory                                                                                                                                                                     | processor supports protection of program<br>memory                                                                                                             |  |

| Properties        | Adaptability                        | modular PLC systems allows to add further<br>modules (I/O, special function,), other<br>devices can be added via bus interface                                                   | full control of SW,<br>custom main board allows adaptations, but<br>these changes require redesigns of the<br>hardware (incl. verification and<br>certification)                                                       | full control of SW,<br>full control of HW, but changes require<br>redesign (incl. verification and certification)                                              |  |

|                   | Energy efficiency                   | COTS devices with acceptable energy efficiency are available                                                                                                                     | the custom made design and the selection<br>of a suitable processor board allows an<br>optimized design                                                                                                                | stand by <0,4W => low power controller in<br>combination with suitable HW and SW<br>design (sleep modi)                                                        |  |

|                   | Size & Weight                       | no specific requirements                                                                                                                                                         | size of PCB determined by 10" screen (not<br>critical)<br>no specific weight requirements                                                                                                                              | critical => only achievable with custom<br>design                                                                                                              |  |

| time              | e to market                         | fast (weeks)                                                                                                                                                                     | medium (months),<br>with COTS processor board, the SW<br>development can start before custom made<br>HW is ready,<br>risk of design iterations                                                                         | medium-high (months),<br>with evaluation board, the SW development<br>can start before custom made HW is ready,<br>risk of design iterations                   |  |

| custor            | ner perception                      | selected brand of COTS device supports<br>image of high quality product                                                                                                          |                                                                                                                                                                                                                        | customized solution allows to meet the targets for size and product price                                                                                      |  |

Figure 3. Case Study

- components as memory chips change frequently. In COTS approach, the qualification of new chips is done by supplier.

- an approach of a complete COTS user terminal in combination with an interface converter was resulting in a significantly higher product price.

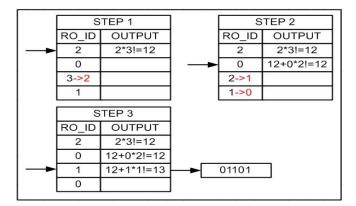

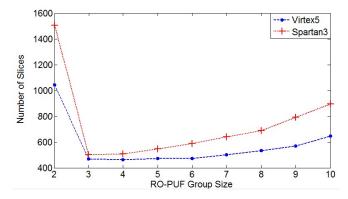

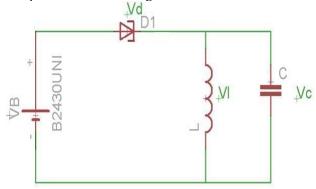

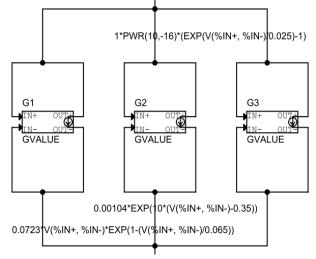

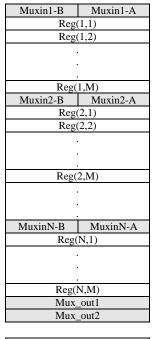

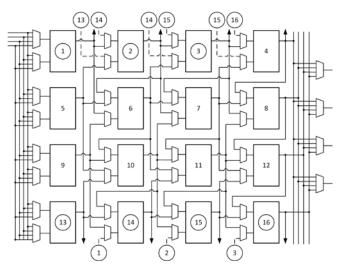

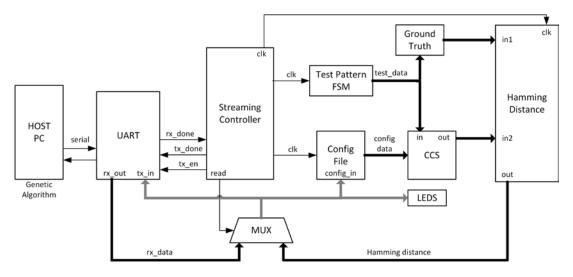

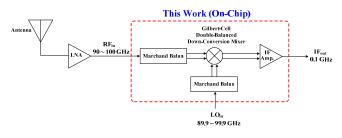

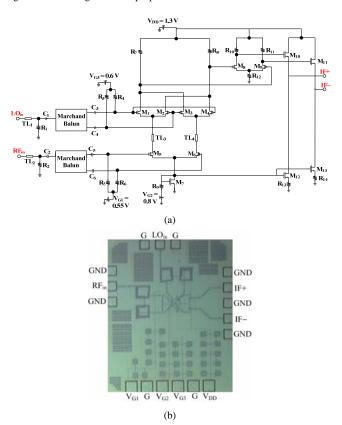

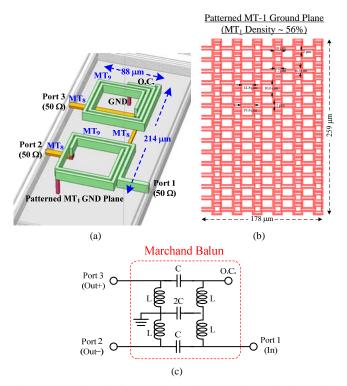

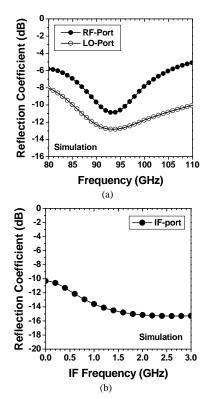

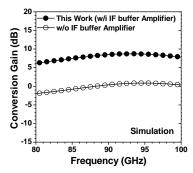

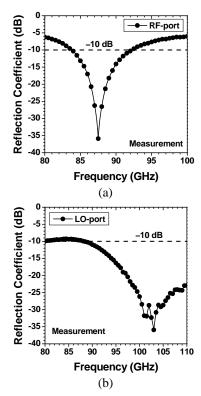

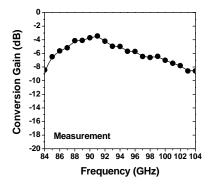

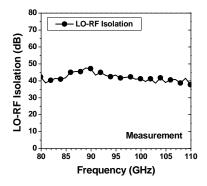

Also the remaining cost related factors show no disadvantage of this approach compared to a full custom made design. With respect to time to market this approach benefits from the COTS components in comparison to the CM approach, as a major part of the design could be implemented as a pretested module. The product properties are influenced as follows: