# **CENICS 2011**

The Fourth International Conference on Advances in Circuits, Electronics and Micro-electronics

ISBN: 978-1-61208-150-2

August 21-27, 2011

Nice/Saint Laurent du Var, France

**CENICS 2011 Editors**

Vladimir Privman, Clarkson University - Potsdam, USA

Martin Horauer, University of Applied Sciences Technikum Wien, Austria

# **CENICS 2011**

# Foreword

The Fourth International Conference on Advances in Circuits, Electronics and Micro-electronics (CENICS 2011), held between August 21-27, 2011 in Nice/Saint Laurent du Var, France, continued a series of events initiated in 2008, capturing the advances on special circuits, electronics, and micro-electronics on both theory and practice, from fabrication to applications using these special circuits and systems. The topics cover fundamentals of design and implementation, techniques for deployment in various applications, and advances in signal processing.

Innovations in special circuits, electronics and micro-electronics are the key support for a large spectrum of applications. The conference is focusing on several complementary aspects and targets the advances in each on it: signal processing and electronics for high speed processing, micro- and nano-electronics, special electronics for implantable and wearable devices, sensor related electronics focusing on low energy consumption, and special applications domains of telemedicine and ehealth, bio-systems, navigation systems, automotive systems, home-oriented electronics, bio-systems, etc. These applications led to special design and implementation techniques, reconfigurable and self-reconfigurable devices, and require particular methodologies to be integrated on already existing Internet-based communications and applications. Special care is required for particular devices intended to work directly with human body (implantable, wearable, ehealth), or in a human-close environment (telemedicine, house-oriented, navigation, automotive). The mini-size required by such devices confronted the scientists with special signal processing requirements.

We take here the opportunity to warmly thank all the members of the CENICS 2011 technical program committee as well as the numerous reviewers. The creation of such a broad and high quality conference program would not have been possible without their involvement. We also kindly thank all the authors that dedicated much of their time and efforts to contribute to the CENICS 2011. We truly believe that thanks to all these efforts, the final conference program consists of top quality contributions.

This event could also not have been a reality without the support of many individuals, organizations and sponsors. We also gratefully thank the members of the CENICS 2011 organizing committee for their help in handling the logistics and for their work that is making this professional meeting a success.

We hope the CENICS 2011 was a successful international forum for the exchange of ideas and results between academia and industry and to promote further progress in the area of circuits, electronics, and micro-electronics.

We hope Côte d'Azur provided a pleasant environment during the conference and everyone saved some time for exploring the Mediterranean Coast.

# **CENICS 2011 Chairs**

# **Advisory Chairs**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

# **Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

# **Industry Liaison Chairs**

Falk Salewski, Lacroix Electronics, Germany

**Special Area Chairs**

**Formalisms** Peeter Ellervee, Tallinn University of Technology, Estonia

# **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

# Sensors

Yulong Zhao, Xi'an Jiaotong University, China

# **CENICS 2011**

# Committee

# **CENICS Advisory Chairs**

Vladimir Privman, Clarkson University - Potsdam, USA Sergey Y. Yurish, Technical University of Catalonia (UPC-Barcelona), Spain Martin Horauer, University of Applied Sciences Technikum Wien, Austria Adrian Muscat, University of Malta, Malta

# **CENICS 2011 Research/Industry Chairs**

Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India

# **CENICS 2010 Industry Liaison Chairs**

Falk Salewski, Lacroix Electronics, Germany

# **CENICS 2011 Special Area Chairs**

Formalisms Peeter Ellervee, Tallinn University of Technology, Estonia

# **Application-oriented**

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain

# Sensors

Yulong Zhao, Xi'an Jiaotong University, China

# **CENICS 2011 Technical Program Committee**

Mohammad Amin Amiri, Iran University of Science and Technology, Iran Ermeson Andrade, Universidade Federal de Pernambuco (UFPE), Brazil Theodore A. Antonakopoulos, University of Patras, Greece Tawfik R. Arabi, Intel Corporation, USA Lotfi Bendaouia, CDTA, Algeria Javier Calpe-Maravilla, Universidad de Valencia, Spain Jinwook (Will) Chung, Massachusetts Institute of Technology (MIT), USA David Cordeau, LAII-IUT Angoulême, France Pasquale Corsonello, University of Calabria, Italy Marc Daumas, Université de Perpignan, France John D. Davis, Microsoft Research - Silicon Valley, USA Javier Diaz-Carmona, Technological Institute of Celaya, Mexico Peeter Ellervee, Tallinn University of Technology, Estonia

Josu Etxaniz Marañon, University of the Basque Country / Universidad del País Vasco / Euskal Herriko Unibertsitatea - Bilbao, Spain Ykhlef Faycal, Centre de Développement des Technologies Avancées, Algeria Sérgio Adriano Fernandes Lopes, Universidade do Minho, Portugal Francisco V. Fernández, IMSE, CSIC and University of Sevilla, Spain Dorian Gachon, Université de Perpignan, France Luis Gomes, Universidade Nova de Lisboa, Portugal Abdulrahman Hamed, Laboratoire d'Instrumentation Électronique de Nancy (LIEN)-Nancy University, France Petr Hanácek, Brno University of Technology, Czech Republic Mohamed Henini, University of Nottingham, UK Martin Horauer, University of Applied Sciences Technikum Wien, Austria Paloma R. Horche, Universidad Politécnica de Madrid, Spain Liudi Jiang, University of Southampton, UK Kenneth Blair Kent, University of New Brunswick, Canada Tomas Krilavicius, Vytautas Magnus University - Kaunas & Baltic Institute of Advanced Technologies -Vilnius, Lithuania Kevin Lee, Murdoch University, Western Australia Junghee Lee, Georgia Institute of Technology, USA Kerstin Lemke-Rust, University of Applied Sciences Bonn-Rhein-Sieg, Germany Diptarka Majumdar, Sun Chemical Corporation - Carlstadt, USA Ka Lok Man, Xi'an Jiaotong-Liverpool University, China Jose Carlos M. M. Metrolho, Polytechnic Institute of Castelo Branco, Portugal Jan Mink, 2M Engineering - Veldhoven, The Netherlands Bartolomeo Montrucchio, Politecnico di Torino, Italy Adrian Muscat, University of Malta, Malta Arnaldo Oliveira, Universidade de Aveiro, Portugal Adam Pawlak, Silesian University of Technology - Gliwice, Poland Stefania Perri, University of Calabria, Italy Vladimir Privman, Clarkson University - Potsdam, USA Càndid Reig, University of Valencia, Spain Falk Salewski, Lacroix Electronics, Germany Arvind K. Srivastava, NanoSonix Inc., USA Ephraim Suhir, University of California - Santa Cruz, USA Olivier Tesson, NXP Semiconductors, France Koldo Tomasena, CEIT & Universidad de Navarra, Spain Félix Torán, European Space Agency, Spain Igone Velez, Universidad de Navarra, Spain Manuela Vieira, ISEL, Portugal Chin-Long Wey, National Central University, Taiwan Ravi M. Yadahalli, PES Institute of Technology & Management - Karnataka, India Jianhua (Joshua) Yang, Hewlett Packard Laboratories - Palo Alto, USA Sergey Y. Yurish, IFSA - Barcelona, Spain David Zammit-Mangion, University of Malta, Malta Yulong Zhao, Xi'an Jiaotong University, China

# **Copyright Information**

For your reference, this is the text governing the copyright release for material published by IARIA.

The copyright release is a transfer of publication rights, which allows IARIA and its partners to drive the dissemination of the published material. This allows IARIA to give articles increased visibility via distribution, inclusion in libraries, and arrangements for submission to indexes.

I, the undersigned, declare that the article is original, and that I represent the authors of this article in the copyright release matters. If this work has been done as work-for-hire, I have obtained all necessary clearances to execute a copyright release. I hereby irrevocably transfer exclusive copyright for this material to IARIA. I give IARIA permission or reproduce the work in any media format such as, but not limited to, print, digital, or electronic. I give IARIA permission to distribute the materials without restriction to any institutions or individuals. I give IARIA permission to submit the work for inclusion in article repositories as IARIA sees fit.

I, the undersigned, declare that to the best of my knowledge, the article is does not contain libelous or otherwise unlawful contents or invading the right of privacy or infringing on a proprietary right.

Following the copyright release, any circulated version of the article must bear the copyright notice and any header and footer information that IARIA applies to the published article.

IARIA grants royalty-free permission to the authors to disseminate the work, under the above provisions, for any academic, commercial, or industrial use. IARIA grants royalty-free permission to any individuals or institutions to make the article available electronically, online, or in print.

IARIA acknowledges that rights to any algorithm, process, procedure, apparatus, or articles of manufacture remain with the authors and their employers.

I, the undersigned, understand that IARIA will not be liable, in contract, tort (including, without limitation, negligence), pre-contract or other representations (other than fraudulent misrepresentations) or otherwise in connection with the publication of my work.

Exception to the above is made for work-for-hire performed while employed by the government. In that case, copyright to the material remains with the said government. The rightful owners (authors and government entity) grant unlimited and unrestricted permission to IARIA, IARIA's contractors, and IARIA's partners to further distribute the work.

# **Table of Contents**

| Efficient Implementations of Radix-4 Parallel-Prefix Trees<br>Stefania Perri and Pasquale Corsonello                                                                                                  | 1  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Design and Analysis of a Dual Loop CDR using Maneatis Delay Cell VCO<br>Khalil Mahmoud, Dhurga Devi, and P. Ramakrishna                                                                               | 6  |

| A Flexible Sensor-mat to Automate the Process of People Counting<br>Christof Kutschera, Martin Horauer, Markus Ray, Daniel Steinmair, and Peter Gorski                                                | 13 |

| Interaction of Semiconductor Laser Chirp with Fiber Dispersion: Impact on WDM Directly Modulated System<br>Performance<br>Paloma R. Horche, Carmina del rio Campos, and Alfredo Martin Minguez        | 17 |

| Step-by-Step Design and EM Modeling of a 3D Solenoid-based 4 GHz Band-pass Filter (BPF) using Through Silicon Vias Olivier Tesson, Stephane Charlot, and Magali Duplessis                             | 23 |

| Comparison of Three Impedance Analysers Implemented on FPGA Circuits<br>Abdulrahman Hamed, Etienne Tisserand, Patrick Schweitzer, and Yves Berviller                                                  | 29 |

| Design of Reconfigurable Quad-band CMOS Class AB Power Amplifier employing MEMS Variable Capacitors<br>in 0.18µm Technology<br>Mansour Fall, Frederic Domingue, Siamak Fouladi, and Raafat R. Mansour | 34 |

| The Impact of High Dielectric Permittivity of 2-D Numerical Modeling Nanoscale SOI Double-Gate Mosfet<br>Using Nextnano Simulator<br>Samia Slimani and Bouaza Djellouli                               | 38 |

# **Efficient Implementations of Radix-4 Parallel-Prefix Trees**

Stefania Perri, Pasquale Corsonello Department of Electronics, Computer Science and Systems DEIS-UNICAL perri@deis.unical.it; p.corsonello@unical.it

*Abstract*—This paper presents novel dynamic circuits purposedesigned to realize parallel-prefix adder trees with computational delay and power consumption lower than the conventional domino logic implementations. The proposed circuits increase speed by reducing the complexity of the pulldown networks of each dynamic gate; and save power by reducing the number of dynamic stages within the overall structure of the generic parallel-prefix tree. When the ST 45nm 1V CMOS technology is used, 32-bit radix-4 Brent-Kung, Han-Carlson and Ladner-Fischer trees designed as proposed here achieve, respectively, a computational delay of 148ps, 129.6ps and 117.2ps; dissipate 194fJ, 240fJ and 209fJ; and shows a silicon area requirement of 160um<sup>2</sup>, 190um<sup>2</sup> and 170um<sup>2</sup>.

Keywords- Adders; VLSI circuits; parallel-prefix trees.

# I. INTRODUCTION

Addition is the basic operation of any digital system. Therefore, the design of high-speed, low-power and area efficient binary adders always receives a great deal of attention. Among the hundreds adder architectures known in the literature, when high performances are mandatory, parallel-prefix trees are generally preferable [1-12].

Optimizing a parallel-prefix tree architecture and its transistor-level implementation for a specific design is not trivial since the designer has to choose: i) the radix-of the carry tree (i.e. the number of carries grouped in each step of the computation); ii) the tree architecture; iii) the logic style. As is well known, all these choices are crucial for both speed and power. In fact, higher radices determine a lower number of stages needed in the tree to compute the output carry signals, but they require more complex gates. Furthermore, at a given radix r, dense architectures, such as the Kogge-Stone tree [13], reach the minimum logic depth, but they require a large number of gates and consume a large amount of power. On the contrary, sparse trees, like the Brent-Kung [14], the Han-Carlson [15] and the Ladner-Fischer [16], do not assure obtaining the minimum logic depth, but they save hardware resources and power. Last but not least, logic style significantly affects delay and energy. As shown in [5-7, 12], parallel-prefix trees realized using dynamic domino logic achieve higher speed performances at the expense of consumed energy; whereas, using static logics lowers power consumption, but sacrifices computational speed.

This paper proposes a novel approach to optimize the implementation of the basic logic modules, namely the preprocessing stage and the associative dot operator, typically used within parallel-prefix adders. The basic idea exploited in the proposed designs consists of: 1) increasing speed by reducing the complexity of the pull-down networks (PDNs) of each dynamic gate; and 2) saving power by reducing the number of dynamic stages within the overall structure of the generic parallel-prefix tree.

Further advantages are taken by using the compound domino logic (CDL) [17]. The latter was used as an efficient alternative to the purely dynamic and static logic design styles also in [1], [5], [6], and [12]. The CDL replaces the inverter stages used in common domino circuits to invert the precharged nodes with more complex inverting static CMOS gates.

Purpose-designed CDL gates are proposed to realize efficient radix-4 parallel-prefix adder trees. Gates designed with the approach proposed here are implemented using the ST 45nm 1V CMOS technology.

The novel circuits were used to implement 32-bit parallel-prefix trees based on the Brent-Kung, Han-Carlson and Ladner-Fischer architectures. Comparison with conventional domino counterparts demonstrate that, due to the innovations introduced, up to ~40% lower computational delay is achieved with up to ~44.7% lower energy consumption and up to ~44.8% lower silicon area requirement.

The paper is organized as follows: in Section 2, a brief background on the parallel-prefix adder trees is provided and conventional domino gates implementations are also shown; the novel circuits are then described in Section 3 where comparison results are also presented and discussed; finally, conclusions are drawn.

# II. BACKGROUND

Let us consider two *n*-bit addends  $A = a_{n-1} \dots a_0$  and  $B = b_{n-1} \dots b_0$ . A parallel-prefix adder computes the sum  $S = A + B = s_{n-1} \dots s_0$  through the following three steps: i) the preprocessing stage computes the auxiliary signals propagate and generate; ii) the carry propagation stage groups the propagate and generate signals *r* by *r*, with *r* being the radix of the adder; iii) the produced carries are then used by the final stage to calculate the sum bit  $s_i$ , with  $i=n-1,\dots,0$ .

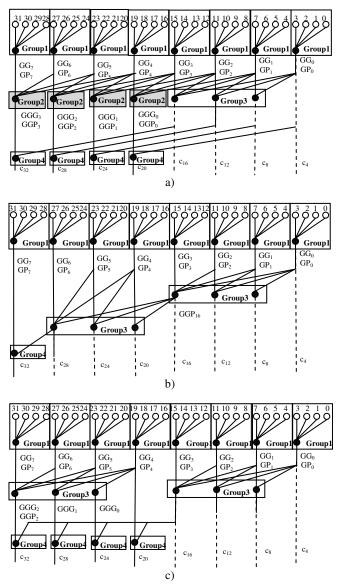

In Fig.1, examples of 32-bit radix-4 parallel-prefix trees are depicted. By observing these examples and others numerous trees known in the literature, it can be easily seen that the basic modules needed to design a parallel-prefix tree are those indicated as Group1, Group2, Group3 and Group4.

Figure 1. Examples of parallel prefix adders: (a) Han-Carlson; (b) Brent-Kung; (c) Ladner-Fischer.

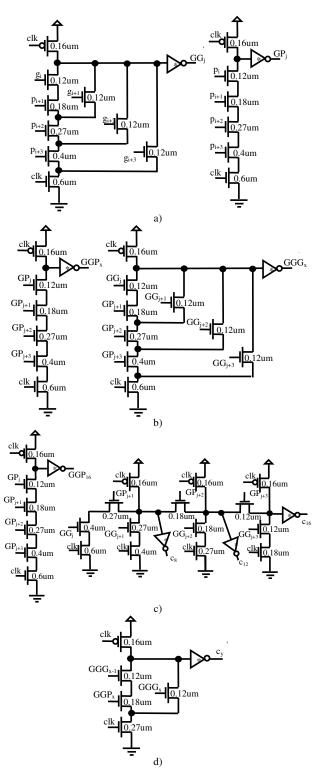

Their conventional domino logic implementations are shown in Fig.2 that also reports transistor widths referred to the ST 45nm 1V CMOS technology. They were obtained considering that 0.12um is the minimum transistor width allowed by the technology used. The minimum size criterion was applied to the elementary 2-input OR and AND gates that are not shown in the Figure, whereas the progressive transistor sizing with a 1.5 tapering factor was exploited within the Manchester carry-chains and gates with higher fan-in. All the inverters on the dynamic nodes are minimum sized with an aspect ratio of 4/3.

The module Group1 of Fig.2a preliminary computes propagate and generate signals at the *i*-th bit position as shown in (1), where i=0,..., n-1.

Figure 2. Conventional implementations of the modules: (a) Group1; (b) Group2; (c) Group3; (d) Group4.

$$p_i = a_i + b_i$$

$$g_i = a_i \cdot b_i$$

(1)

Propagate and generate signals are then grouped four by four implementing the classical carry-look-ahead equations reported in (2), where  $j = \frac{i}{4}$ , and j=0,...,7.

$$GP_{j} = p_{i+3} \cdot p_{i+2} \cdot p_{i+1} \cdot p_{i}$$

$$GG_{j} = g_{i+3} + p_{i+3} \cdot g_{i+2} + p_{i+3} \cdot p_{i+2} \cdot g_{i+1} + (2)$$

$$+ p_{i+3} \cdot p_{i+2} \cdot p_{i+1} \cdot g_{i}$$

The module Group2 is used to implement equations (3), where x=j-1, and x=0,...,3 for the tree in Fig.1a.

$$GGP_{x} = GP_{j+3} \cdot GP_{j+2} \cdot GP_{j+1} \cdot GP_{j}$$

$$GGG_{x} = GG_{j+3} + GP_{j+3} \cdot GG_{j+2} + GP_{j+3} \cdot GP_{j+2} \cdot GP_{j+1} \cdot GG_{j}$$

$$(3)$$

For all the referred tree architectures, the carry signals  $c_8$ ,  $c_{12}$  and  $c_{16}$  are computed by the module Group3 that, as illustrated in Fig.2c, also provides the grouped propagate signal  $GGP_{16}$ . The same module is used in the Ladner-Fischer sparse tree of Fig.1c also to compute the grouped generate signals  $GGG_2$ ,  $GGG_1$ ,  $GGG_0$  and the grouped propagate signal  $GGP_2$ , and in the Brent-Kung architecture of Fig.1b to compute the carry signals  $c_{20}$ ,  $c_{24}$  and  $c_{28}$ .

Some of the final carries of the referred 32-bit trees are computed further grouping the signals  $GGG_x$  and  $GGP_x$  two by two following the classical carry-look-ahead logic shown in (4) and implemented by the module Group4 depicted in Fig.2d.

$$c_{v} = GGG_{r} + GGP_{r} \cdot GGG_{r-1} \tag{4}$$

Equations (1)-(3) are specialized for 32-bit radix-4 trees. However, they can be easily extended to different wordlengths and radices.

#### III. THE NOVEL CIRCUITS

This Section proposes novel transistor-level implementations of the basic modules used within parallelprefix trees. The novel circuits are purpose-designed to increase speed performance and to reduce energy consumption with respect to their conventional domino logic counterparts. The main innovations here introduced consist in: i) reducing the number of dynamic nodes within each module with the objective of reducing the power consumption and ii) simplifying the pull-down networks (PDNs) of each dynamic stage to reduce the computational delay.

The number of dynamic nodes within each module is reduced mainly by avoiding the computation of useless intermediate signals. To better explain how this is possible let us examine the module Group1 implemented with the conventional domino logic as illustrated above in Fig.2a. It is easy to verify that the computation of the generic  $GG_j$  and  $GP_j$  signals involves ten dynamic nodes: four belong to the 2-input OR gates computing the propagate signals  $p_i$ ,  $p_{i+1}$ ,  $p_{i+2}$  and  $p_{i+3}$ ; further four dynamic nodes belong to the 2input AND gates producing the generate signals  $g_i$ ,  $g_{i+1}$ ,  $g_{i+2}$ and  $g_{i+3}$ ; finally, two dynamic nodes are used within the gates required to group 4 by 4 the propagate and generate signals.

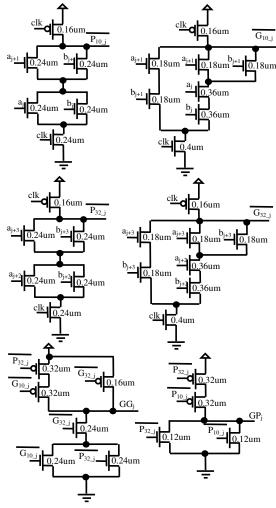

The novel module Group1\_new was designed to produce only one propagate and one generate signal by each two bit positions. As visible from the transistor-level implementation illustrated in Fig.3, in this way only two propagate intermediate signals,  $\overline{P_{32_J}}$  and  $\overline{P_{10_J}}$ , and two generate intermediate signals,  $\overline{G_{32_J}}$  and  $\overline{G_{10_J}}$ , are required, thus reducing the overall number of dynamic nodes involved in the computation of the signals  $G_{G_j}$  and  $GP_j$  to four. It can be observed that, in order to simplify the PDNs of dynamic stages, the CDL style is exploited and static CMOS inverters used in conventional dynamic circuits to achieve the domino behavior are replaced with more complex static CMOS gates.

Figure 3. The Group1\_new module.

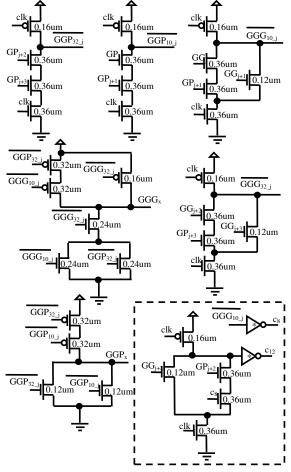

The basic gates used in the novel modules Group2\_new and Group3\_new are illustrated in Fig.4. There,  $GGG_x$  and  $GGP_x$  correspond to  $c_{16}$  and  $GGP_{16}$  in Group3\_new. The latter also uses the gates enclosed in the dashed box to compute the carry signals  $c_8$  and  $c_{12}$ . The approach used to design these gates does not reduce the number of dynamic nodes with respect to the conventional implementations, but it allows the PDNs of dynamic stages to be simplified. In fact, from Fig.4 it can be seen that the PDNs of dynamic stages inside the modules Group2\_new and Group3\_new contain no more than three series transistors, whereas the conventional modules Group2 and Group3 of Figs.2b and 2c use PDNs with up to five series transistors.

Due to its simplicity, for the module Group4 depicted in Fig.2d a CDL implementation does not make sense.

Finally, it is worth emphasizing that the transistors of the novel circuits are sized ensuring that the input capacitances of a parallel-prefix tree designed as proposed here are mainly unchanged with respect to the conventional implementation. In this way, front-end modules providing the operands A and B, are not influenced by the adopted innovations.

# A. Parallel-prefix trees implementation and comparison results

The novel modules described above were exploited to realize the 32-bit radix-4 architectures depicted in Fig.1. In the following, the Han-Carlson, Brent-Kung and Ladner-Fischer trees realized using the novel modules are named HC\_new, BK\_new and LF\_new, respectively.

For purposes of comparison, conventional domino logic implementations of the referenced trees (in the following named HC\_conv, BK\_conv and LF\_conv) were also carried out and they were compared to the novel implementations in terms of worst-case delay  $T_W$  and energy consumption. Prelayout Corner Analysis was performed loading each carry output signal with a 1fF capacitance. The latter was chosen referring to the input capacitance of a positive edge-triggered D flip-flop with 9x drive strength available within the standard cells library of the used 45nm technology.

TABLE I. PRE-LAYOUT SIMULATION RESULTS

| Tree    |       | $T_W[ps]$ |       | F     | Energy [pJ] |       |

|---------|-------|-----------|-------|-------|-------------|-------|

|         | TT    | FF        | SS    | TT    | FF          | SS    |

| HC_conv | 126.4 | 100.3     | 158.5 | 0.296 | 0.332       | 0.282 |

| HC_new  | 115   | 89.7      | 145.7 | 0.214 | 0.255       | 0.192 |

| BK_conv | 179   | 142.1     | 225   | 0.262 | 0.295       | 0.249 |

| BK_new  | 134.6 | 104.6     | 170.8 | 0.185 | 0.223       | 0.165 |

| LF_conv | 129   | 101.8     | 161.4 | 0.27  | 0.303       | 0.257 |

| LF_new  | 103.3 | 80.2      | 130.9 | 0.193 | 0.231       | 0.173 |

TABLE II. POST-LAYOUT SIMULATION RESULTS

| Tree    | $T_W[ps]$ |       | Energy [pJ] |       |       | Area  |          |

|---------|-----------|-------|-------------|-------|-------|-------|----------|

|         | TT        | FF    | SS          | TT    | FF    | SS    | $[um^2]$ |

| HC_conv | 175.7     | 138.3 | 223.8       | 0.392 | 0.416 | 0.381 | 320      |

| HC_new  | 129.6     | 101   | 164         | 0.24  | 0.29  | 0.231 | 190      |

| BK_conv | 248       | 196.6 | 313.5       | 0.351 | 0.373 | 0.341 | 290      |

| BK_new  | 148       | 115   | 188.5       | 0.194 | 0.221 | 0.186 | 160      |

| LF_conv | 175.4     | 139.2 | 222.3       | 0.36  | 0.383 | 0.351 | 306      |

| LF_new  | 117.2     | 91.5  | 148.5       | 0.209 | 0.248 | 0.2   | 170      |

Simulation results reported in Table I demonstrate that, for all the examined trees, the novel circuits lead to consistent speed improvement and energy reduction.

All the above compared parallel-prefix trees were laid out using the full-custom layout approach. Results obtained through the post-layout Corner Analysis are reported in Table II, which demonstrates how the advantages introduced by the novel circuits are maintained also in the laid out trees. As an example, the BK\_new tree exhibits computational delay, energy consumption and silicon area occupancy ~40%, ~44.7% and ~44.8% lower than the conventional domino implementation BK\_conv. Similar improvements are achieved also for the Han-Carlson and Ladner-Fischer parallel-prefix trees, thus demonstrating that the proposed circuits are advantageous in several parallelprefix architectures.

Figure 4. The novel modules Group2\_new and Group3\_new.

# IV. CONCLUSIONS

A novel design approach was presented to implement efficient sparse parallel-prefix adder trees using nanometer technologies. The basic idea exploited in the proposed designs consists of: 1) reducing the complexity of the pulldown networks (PDNs) of each dynamic gate; and 2) minimizing the number of dynamic nodes within the overall structure of the generic parallel-prefix tree. The innovations here introduced allow reducing both the computational time and the average power consumption with respect to conventional domino logic implementations.

As an example, a 32-bit radix-4 Brent-Kung tree designed as proposed here achieves a computational delay of only 148ps, dissipates just 194fJ and occupies a  $160 \text{ um}^2$  silicon area, that are ~40%, ~44.7% and ~44.8% lower than the conventional domino implementation.

#### REFERENCES

- J.Park, H.C.Ngo, J.A.Silberman, S.H.Dhong, "470ps 64bit Parallel Binary Adder", *Proc. IEEE Symposium on VLSI Circuits*, June 2000, Honolulu, Hawaii, pp.192-193.

- [2] P.Corsonello, S.Perri, M.Margala, "Efficient Addition Circuits for Modular Design of Processors-in-Memory", *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol.52, n°8, pp.1557-1567, 2005.

- [3] F.Frustaci, M.Lanuzza, P.Zicari, S.Perri, P.Corsonello, "Designing High-Speed Adders in Power-Constrained Environments", *IEEE Transactions on Circuits and Systems II: Express Briefs*, Vol.56, n°2, pp.172-176, 2009.

- [4] S.Das, S.P.Khatri, "A Novel Hybrid Parallel-Prefix Adder Architecture With Efficient Timing-Area Characteristic", *IEEE Transactions on VLSI Systems*, Vol.16, n°3, pp.326-331, 2008.

- [5] V.G.Oklobdzija, B.R.Zeydel, H.Q.Dao, S.Mathew, R.Krishnamurthy, "Comparison of High-Performance VLSI Adders in the Energy-Delay Space", *IEEE Transactions on VLSI Systems*, Vol.13, n°6, pp.754-758, 2005.

- [6] R.Zlatanovici, S.Kao, B.Nikolic, "Energy-Delay Optimization of 64bit Carry-Lookahead Adders with a 240ps 90nm CMOS Design Example", *IEEE Journal of Solid-State Circuits*, Vol.44, n°2, pp.569-583, 2009.

- [7] J.Grad, J.E.Stine, "Low Power Binary Addition Using Carry Increment Adders", Proc. of the IEEE International Symposium on Circuits and Systems, May 2006, Island of Kos, Greece, pp.17-20.

- [8] G.Dimitrakopoulos, D.Nikolos, "High-Speed Parallel-Prefix VLSI Ling Adders", *IEEE Transactions on Computers*, vol.54, n°2, pp.225-231,2005.

- [9] F.Liu, F.F.Forouzandeh, O.A.Mohamed, G.Chen, X.Song, Q.Tan, "A Comparative Study of Parallel Prefix Adders in FPGA Implementation of EAC", *Proc. of the EUROMICRO Conference on Digital System Design, Architetcures, Methods and Tools*, August 2009, Patras, Greece, pp.281-286.

- [10] S.Das, S.P.Khatri, "A Novel Hybrid Paralle-Prefix Adder Architecture With Efficient Timing-Area Characteristic", *IEEE Transactions on VLSI Systems*, vol.16, n°3, pp.326-331, 2008.

- [11] S.Ghosh, K.Roy, "Novel Low Overhead Post-Silicon Self-Correction Technique for Parallel Prefix Adders Using Selective Redundancy and Adaptive Clocking", *IEEE Transactions on VLSI Systems*, Forthcoming.

- [12] B.R.Zeydel, D.Baran, V.G.Oklobdzija, "Energy-Efficient Design Methodologies: High-Performance VLSI Adders", *IEEE Journal of Solid-State Circuits*, vol.45, n°6, pp.1220-1233, 2010.

- [13] P.M.Kogge, H.S.Stone, "A Parallel Algorithm for the Efficient Solution of a General Class of Recurrence Equations", *IEEE Transactions on Computers*, Vol.C-22, n°8, pp.786-793, 1973.

- [14] R.P.Brent, H.T.Kung, "A regular layout for parallel adders", *IEEE Transactions on Computers*, vol.C-31, n°3, pp.260-264, 1982.

- [15] T.Han, D.A.Carlson, "Fast area-efficient VLSI adders", Proc. IEEE Symposium on Computer Arithmetic, May 1987, Como, Italy, pp.49-56.

- [16] R.E.Ladner, M.J.Fischer, "Parallel Prefix Computation", Journal of the ACM, Vol.27, n°4, pp.831-838, 1980.

- [17] K.Bernstein, K.M.Carrig, C.M.Durham, P.R.Hansen, D. Hogenmiller, E.J.Nowak, N.R.Rohrer, *High-Speed CMOS Design Styles*, Kluwer Academic, 1998.

# Design and Analysis of a Dual Loop CDR using Maneatis Delay Cell VCO

Khalil Ibrahim Mahmoud, J. Dhurga Devi, and P.V. Ramakrishna Department of Electronics and Communication Engineering College of Engineering, Anna University, Chennai, INDIA 600025 khalilaljabory@gmail.com, j\_dhurgadevi@annauniv.edu, pvramakrishna@annauniv.edu

Abstract — Clock and Data Recovery (CDR) circuits have been used extensively in the receivers of optical communication systems, and a variety of applications of inter and intra chip communications. The primary design/performance metrics of CDR circuits are clock jitter, lock range, acquisition time, power consumption, silicon area, and noise immunity. The main source of jitter is the power supply noise. The present paper investigates the effects of power supply noise on the jitter performance of the well known dual loop architecture of CDR system. In order to improve the jitter performance of the dual loop CDR system, the VCO alone is replaced by the selfbiased Maneatis VCO which is well known for its immunity to power supply noise and process variations. The Maneatis VCO is widely used for microprocessors PLL systems but it is rarely used in CDR systems. The combination of the dual loop architecture and self-biased Maneatis VCO together provides the benefits of both schemes.

Simulations were then carried out systematically to determine the capability of the proposed CDR circuit to tolerate power supply noise. The results presented in this paper show that while the conventional dual loop architecture cannot tolerate more than 20mV@10MHz noise on power supply terminal, the proposed CDR architecture can tolerate up to 200mV@10MHz noise on the power supply without degradations in jitter performance.

#### Keywords- CDR, PLL, VCO, Jitter, Power Supply Noise.

## I. INTRODUCTION

During the past few decades, the CDR circuits have played an important role in a wide range of applications such as Gigabit Passive Optical Network (GPON), Gigabit Ethernet Passive Optical Network (GEPON), Synchronous Optical Network (SONET), optical transmission receiver, chip-chip interconnections, DDR, System on Chip (SOC), serial link communications, and PCI. The CDR circuits are normally used to extract the clock embedded in the received data and used to re-time and re-sample the received (distorted) data for further synchronous processing.

The most important metric of CDR system performance is the jitter on the recovered clock, and it represents the deviations of the clock transitions from the ideal one. The state of the art CDR circuit architectures, and the trade-offs and techniques for reducing the jitter are discussed in recent tutorials [3]-[6]. Of late, with the increased integration of analog and digital functions on the same chip, immunity to power supply noise has emerged as a very important design constraint. Several studies on the mitigation of power supply noise on PLLs have been reported in [7]-[10]. In addition to using differential topologies, some of these studies suggest the use of regulators as common techniques used to mitigate the power supply noise. The design of PLLs considering immunity to power supply noise as a design constraint is presented in [9] and considers variants of the Maneatis VCO [11, 12] in the context of PLLs and their sensitivities to power supply noise. A fast Matlab simulation procedure for evaluating the impact of power supply noise on CDR system has been described in [10].

Very few studies on the mitigation of power supply noise for CDRs have been reported in the literature. The present work addresses this particular aspect of CDR circuits, specifically in the context of dual loop delay interpolating architectures. Although there are many architectural choices, the dual loop delay interpolating CDR described in [1]-[3] is chosen for the present study since this is considered as one of the important architectures for realizing CDR circuits with a wide operating frequency range while at the same time providing low jitter.

The symmetric load, self-biased Maneatis VCO proposed by [11, 12], is well known for its ability to mitigate power supply noise and for this reason and is widely used in many of the state of the art of microprocessor PLLs. The present study investigates the possibilities of using this VCO in CDR circuits. It was observed that the Maneatis VCO as proposed in [11, 12] could not be used as such in the original dual loop CDR architecture since the former had only one control voltage input while the latter required a VCO with a coarse as well as fine control voltage inputs. Hence, in the present study, the bias generator of the self-biased Maneatis VCO from [11, 12] was suitably modified and then was incorporated into the CDR circuit. It is demonstrated in this paper that the modified Maneatis VCO is capable of providing improved performance with respect to power supply noise. Specifically, simulation results show that the proposed scheme tolerates up to seven times the power supply noise than in the conventional dual loop CDR for similar jitter performance.

The present paper is organized as follows. Section 2 presents a brief description and design details of the well-known dual loop delay interpolation CDR. Section 3 discusses the proposed modification of the Maneatis VCO for incorporation into the dual loop CDR design. Section 4 gives the simulation results of noise performance for the delay interpolation dual loop CDR as well as for the proposed modified Maneatis dual loop CDR and in Section 5, the conclusions are presented.

# II. THE DUAL LOOP CDR SYSTEM DESIGN

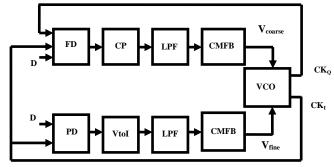

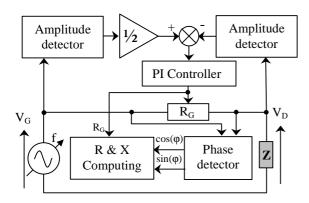

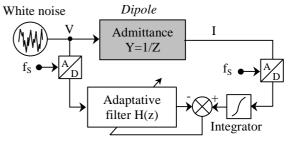

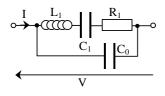

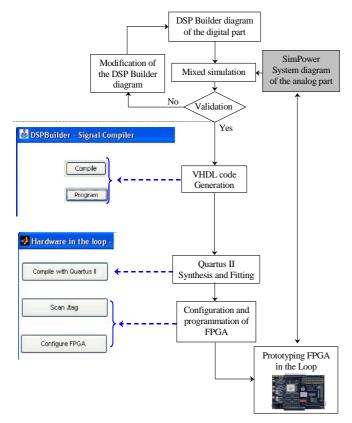

The block diagram of the dual loop delay interpolating CDR is shown in Fig. 1 and is the same as the one presented in [1, 2]. This system will be considered as a reference system against which the performance of the proposed modifications will be compared. The system shown in Fig. 1 consists of a coarse FLL and a fine PLL which operate together on the input data sequence and recover the clock which could be subsequently used for retiming the data.

Figure 1. The Complete CDR System Block Diagram

The FLL provides a coarse acquisition of the clock and operates over a wide frequency range. It comprises of the Frequency Detector (FD), the Charge Pump (CP), the Low Pass Filter (LPF), Common Mode Feedback (CMFB), and a delay interpolating VCO. The FD is realized using a digital quadricorrelator and detects the frequency difference between the input data rate and the internally generated clock by the VCO. The outputs of the FD are the "UP" and "DOWN" pulses that have constant pulse durations and the number of pulses generated in a given time interval depends on the frequency difference. These pulses are fed to the charge pump, where they are converted into proportional charging and discharging currents for the LPF. The details of circuit design for individual blocks of the FD are given in [1, 2] and the same procedure has been adopted for the present work.

The design equations given below are from [1, 2, 13] and are used to determine the LPF parameters of the FLL.

$$\omega_c = \frac{I_{cp}.K_{VCO}.k_p}{2.\pi} \tag{1}$$

$$\omega_z = \frac{\omega_c}{5} = \frac{1}{R_p \cdot C_p} \tag{2}$$

$$\omega_p = 5.\omega_c = \frac{C_p + C_s}{C_p \cdot C_s \cdot R_p}$$

(3)

$$C_{s} = \left[\omega_{p} \cdot R_{p} - \frac{1}{C_{p}}\right]^{-1} \tag{4}$$

The symbols  $\omega_c$ ,  $\omega_z$ ,  $\omega_p$ ,  $\zeta$ , and  $K_{VCO}$  in the above equations represent the crossover frequency, pole frequency,

zero frequency, damping ratio, and VCO gain, respectively. The symbols  $R_p$ ,  $C_p$ , and  $C_s$  represent the shunt resistor, capacitor and parallel smoothing capacitor, respectively.

The PLL in Fig. 1 has a much smaller capture range and operates after the FLL has acquired lock and this combination of FLL lock followed by PLL lock reduces the jitter in the recovered clock considerably. The PLL loop consists of a Phase Detector (PD), a Voltage-to-Current converter (V/I), and the LPF. The PD is an analog sample and holds system which consists of a two sample and hold circuits and a multiplexer. The output of the PD is a differential voltage proportional to the input phase difference. These voltages are converted to proportional currents by the V/I converter and are used as the charging and discharging currents of the LPF of the PLL block.

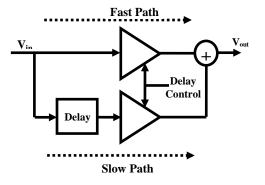

The VCO is a ring oscillator which is common to both FLL and PLL is realized with four delay cells and uses the delay interpolation concept with two paths, the fast path and the slow path. Fig. 2 shows the delay interpolation concept realized in the delay cell. The fast path consists of a differential stage, while the slow path consists of a constant delay stage and a differential stage. The two paths share the same output load. The output current is the sum of the slow and fast currents and is constant. The slow and fast currents are steered differentially depending on the control voltages to maintain constant sum.

Figure 2. Shows the Delay Interpolation Concept

As in the case of the LPF of the FLL, the design procedure for determining the PLL loop filter parameters are adopted from [1, 2, 13] and the design equations are listed below:

$$\tau_2 = \frac{2.\zeta}{\omega_n} \tag{5}$$

$$K = K_{pd} \cdot K_{VCO} \cdot \frac{\pi}{4} \tag{6}$$

$$K = 2.\zeta.\omega_n.\sqrt{\frac{\tau_1}{\tau_2}} + 1 \tag{7}$$

$$\tau_1 = \left( R_{f1} + R_{f2} \right) C \tag{8}$$

$$\tau_2 = R_{f2}.C\tag{9}$$

Where the symbols  $\tau_1$ ,  $\tau_2$ ,  $R_{f1}$ ,  $R_{f2}$ , and c are represent the time constants, series resistor, shunt resistor and capacitor, respectively, of LPF of the PLL. The symbols  $\omega_n$ ,  $\zeta$ , K,  $K_{PD}$ ,  $K_{VCO}$  are the natural frequency, damping ratio, open loop gain, phase detector gain, and VCO gain, respectively and these values can all be determined once the operating frequency, bias currents and technology node of the CMOS process are chosen.

Detailed simulations have been carried to determine the performance of the dual loop delay interpolation CDR with respect to power supply noise. Though the details and quantitative results of these simulations are presented subsequently in Section 4, the conclusion that clearly emerged from these simulations was that the performance of the dual loop delay interpolation CDR was very sensitive to power supply noise, and that one cannot possibly use this CDR without dedicated regulators providing clean power supply to the whole system.

# III. THE MANEATIS DELAY CELL-BASED VCO AND ITS MODIFICATION

It is well known from the PLL literature that the major contribution to jitter (or phase noise) due to power supply noise comes from the VCO block of the PLL, and this was true in the present CDR case as well (quantitative results given in the next section). Since the Maneatis Delay Cellbased VCO is well known for its immunity to power supply noise, the adaptation of this VCO to the dual loop CDR is described next.

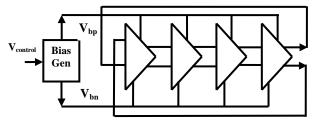

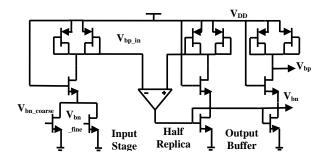

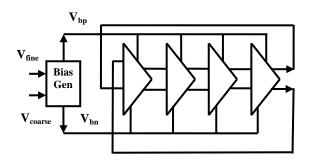

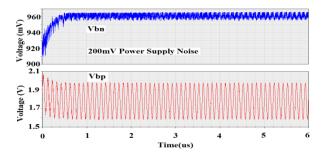

The block diagram of the original Maneatis VCO and its associated bias generator are shown in Fig. 3 and Fig. 4, respectively. The Maneatis VCO shown in Fig. 3 basically comprises of four symmetric load delay cells for which the control voltages come from the bias generator circuit in Fig. 4. The Maneatis Delay cell-based VCO posses two salient features, first is its high supply immunity, and the second is its symmetric load resistance based delay element. The latter enables the VCO to have a wide operating frequency range. The symmetric load resistance can also reject the supply noise (dynamic supply noise rejection) and is obtained by having the lower limit of the voltage swing to be equal to the control voltage itself. Further, for static supply noise rejection, it is required that V<sub>control</sub> track the supply voltage variations and hence it is referenced to (V<sub>DD</sub>) in [11, 12]. From this  $V_{control}$ , one has to generate two bias voltages  $V_{bp}$ and  $V_{bn}$  to be fed to the VCO of Fig. 3. Of these,  $V_{bp}$  tracks the supply voltage changes to keep the load resistance of the delay cell and hence, the output frequency constant. On the other hand, V<sub>hn</sub> is kept independent of supply voltage changes in order to keep the tail current constant. It can be seen that the conventional bias generator shown in Fig. 4 can accept only one control voltage  $V_{\mbox{\scriptsize control}},$  and hence cannot be directly incorporated directly into the dual loop CDR of Fig. 1.

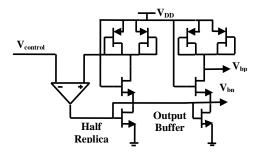

To provide an option for accepting coarse and fine control voltages, the bias generator of the Maneatis VCO has been modified and is shown in Fig. 5. In this modified circuit, the coarse and fine control voltages are provided as gate voltages to two NMOS transistors which act as voltage controlled current sources (tail sources). These currents are summed up to form the drain current of a single PMOS transistor. Since the source of this diode connected PMOS transistor is connected directly to the supply rail, its gate voltage tracks the changes in supply voltage while maintaining the current set by the bottom tail transistors. This gate voltage of the PMOS is then used as part of a feedback loop containing the half replica delay cell to generate the bias voltages V<sub>bp</sub> and V<sub>bn</sub> which are used finally by the delay elements of the VCO. The final block diagram of modified Maneatis delay cell VCO is shown in Fig. 6. The voltage,  $V_{bp}$ , produced by the bias generator tracks the supply voltage and sets the lower limit of the oscillation swing (and the load resistance) to fix the output frequency. On the other hand, since the course  $(V_{bn-coarse})$  and fine control voltages  $(V_{\text{bn-fine}})$  are referenced to the ground terminal, the final voltage  $V_{bn}$ , which determines the tail current in the delay element, keeps the tail current constant.

Figure 3. The original Maneatis VCO

Figure 4. Original Bias Generator

Figure 5. Modified Bias Generator

Figure 6. The proposed modified VCO

The simple modification proposed above for the bias generator provides a method for combining the coarse and fine control voltages while retaining the robustness of the original Maneatis VCO. The sensitivity of this VCO to power supply voltage variations were first assessed and then the VCO was incorporated into the original dual loop CDR scheme of Fig. 1. Using the same system specifications and design equations described earlier in Section 2, the parameters of the LPFs for the FLL and PLL have been determined and are listed in Table I. These parameters are different from those of the delay interpolation VCO because the coarse and fine gains of the modified Maneatis VCO are different from that of delay interpolation VCO.

# IV. SIMULATION RESULTS AND DISCUSSION

In this section, first, quantitative results related to the supply noise performance of the delay interpolating VCO based CDR are presented. Next, simulations results are presented to validate the modification carried out on the Maneatis VCO and also to demonstrate that it can indeed replace the delay interpolation VCO in the original dual loop CDR. Finally, for the modified dual loop CDR, simulation results related to its performance with respect to power supply noise are presented.

All simulations have been carried out using the Cadence Spectre tool. The devices chosen for the simulations are from the 0.35µm CMOS technology libraries from Austriamicrosystems and the various over-drive voltages and bias currents are chosen accordingly. For the present work, a nominal data rate of 833 Mbps is chosen for the CDR, the FLL cross over frequency is chosen as 30MHz, and the charge pump current of the FLL is found to be 125µA. The PLL loop natural frequency  $\omega_n$ , and damping ratio  $\zeta$  are chosen to be 0.5 MHz and 4, respectively. The FLL and PLL LPF parameters have been determined for the above system specifications and given in Table I. For clock recovery simulations, PRBS data of length 2<sup>14</sup> were used as input data to the CDR system.

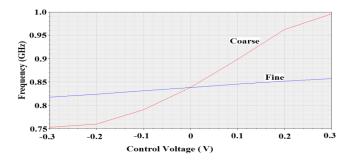

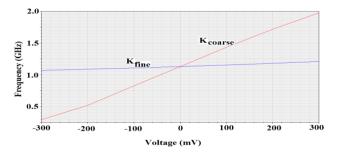

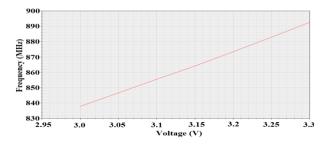

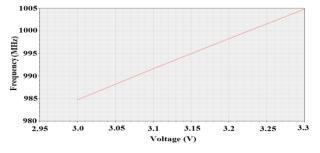

First, the delay interpolation VCO characteristics are given in Fig. 7 where the output frequency dependence on coarse and fine control voltages is shown. The coarse and fine gains are found to be 506MHz/V and 65.9MHz/V, respectively. Similarly, the modified Maneatis VCO circuit was simulated and Fig. 8 shows the corresponding VCO gains plots. The coarse and fine gains were found to be 3GHz/V and 230MHz/V, respectively.

Figure 7. Coarse and Fine Gains of the Delay Interpolation VCO

Figure 8. Coarse and Fine Gains of the Modified Maneatis VCO

Figure 9. The Delay Interpolation VCO Sensitivity to Power Supply Noise

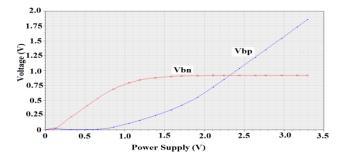

The static supply sensitivity of the delay interpolation VCO is shown in Fig. 9. For a nominal control voltage (Vc=0.74V, Vf=0.74V), it is found to be 185MHz/V and represents 6.6% frequency change for 10% change in the supply. The corresponding static supply sensitivity of the modified Maneatis VCO is shown Fig. 10.

Figure 10. The Modified Maneatis VCO Sensitivity to Power Supply Noise

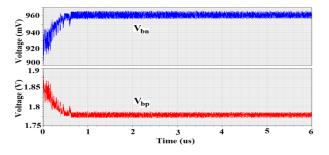

Figure 11. Variations of Vbn and Vbp versus Power Supply Voltage

For a nominal control voltage (Vc=0.95V, Vf=1.05V), it is found to be 67MHz/V and represents 2.4% frequency change for 10% power supply change. The reduction in sensitivity of the modified Maneatis VCO is to be expected and is due to the ability of the bias generator to track the variations of the power supply voltage and is demonstrated in Fig. 11. The variations of V<sub>bn</sub> and V<sub>bp</sub> with respect to V<sub>DD</sub> are plotted in Fig. 11 while maintaining the coarse and fine voltages constant and it can be seen V<sub>bn</sub> is independent of V<sub>DD</sub> while V<sub>bp</sub> tracks V<sub>DD</sub> for static power supply variations. Incidentally, the modified Maneatis VCO also has better power supply sensitivity of 67MHz/V as compared to the value 158MHz/V reported recently in [14], though the latter is for a PLL and for a somewhat higher frequency.

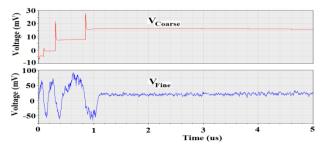

Next, with PRBS data input, clock recovery was carried using two the CDR schemes using clean power supplies. The capture transient showing the evolution of coarse and fine control voltages of the dual loop delay interpolation CDR and the dual loop modified Maneatis CDR are depicted in Fig. 12 and Fig. 13, respectively. For the dual loop delay interpolation CDR, the lock time, the steady state ripple on the fine control voltage, and the recovered clock jitter are 1µsec, 50mV and 4.3psec (0.4%UI), respectively. The corresponding quantities are for the dual loop modified Maneatis CDR are 0.6 µsec, 10mV, and 8.4 psec (0.7% UI), respectively.

Figure 12. CDR Coarse and Fine Control Voltages with Clean Power Supply for Delay Interpolation VCO

Figure 13. CDR Control Voltages with Clean Power Supply for Modified Maneatis VCO

Immunity of the two CDR schemes to power supply noise is characterized by adopting the procedure followed in [11, 12]. Noise sources in the form of sinusoidal signals of different frequencies and amplitudes were superposed on the VDD supply node. The effects of this noise source on the CDR system are measured by two ways. First by measuring the ripple on the differential fine control voltage and the second one is measuring the rms jitter on the recovered clock.

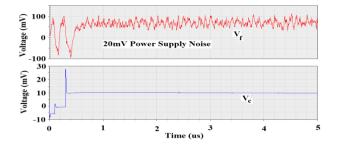

Table II provides the jitter performance of the dual loop delay interpolation CDR with noise injected individually into the power supply node of the different blocks of the CDR. Each column of the table indicates the ripple on the control voltage (after lock) of the dual loop CDR and the jitter on the recovered clock for a specific noise amplitude. It can be seen that the VCO is the most sensitive block and causes maximum degradation of performance. It was also found that the system fails to lock if the noise amplitude is increased beyond 30mV. Fig. 14 shows the differential fine control voltages of the dual loop delay interpolation CDR with noise of 20mV@10MHz on power supply terminal. For comparison, the same parameters are plotted for the dual loop modified Maneatis CDR in Fig. 15 but with a power supply noise of 200mV@10MHz.

Figure 14. CDR Control Voltages with 20mV@10MHz Power Supply Noise for Delay Interpolation VCO

Figure 15. CDR Control Voltages with 200mV@10MHz Power Supply Noise for Modified Maneatis VCO

Finally the jitter performance of the integrated dual loop delay interpolation CDR and the proposed dual loop modified Maneatis CDR are given in Table III. It can be seen that the performance of the latter with 200mv noise is comparable to that of the former with a 30 mV noise on the supply line. The ripple voltage on the control voltage is not listed for the proposed CDR since this tracks the noise on the supply voltage as it is supposed to.

Since the Maneatis VCO and the delay interpolation VCO of the original dual loop scheme are both differential delay cell-based ring oscillators, their power consumption is nearly the same. Since the loop parameters for the proposed scheme have been chosen to be the same as that of the original dual loop scheme, the acquisition time is also nearly the same. Maneatis VCO is inherently known to have a wide range of operating frequencies.

### V. CONCLUSIONS

While it is noted in the literature that the dual loop CDR architecture has certain important desirable features not available in other architectures (see [15] for example), there are no studies reporting its jitter performance with respect to power supply noise. While this might not have been an issue in the older technologies where dedicated external regulators providing clean supplies to the CDR can be assumed, in the context increased integration and System on Chip (SOC) schemes, on chip power supply noise often becomes a serious issue. The results presented in this paper provide three important conclusions. The first is that the original dual loop CDR as proposed in [1] is very sensitive to power supply noise and may require dedicated power supply regulators. The second conclusion is that the original Maneatis delay VCO can indeed be easily modified for incorporation into the dual loop CDR. The third conclusion is that the resulting modified dual loop CDR is capable tolerating nearly 200 mV noise on the supply line without degradation in performance. This in turn indicates that it can be easily integrated onto (SOC) architectures without requiring dedicated supply regulators.

TABLE I. THE PLL AND FLL LPF PARAMETERS

| CDR in Ref. [5] |     |         | CDR wi | th proj          | posed VCC | )       |     |

|-----------------|-----|---------|--------|------------------|-----------|---------|-----|

| PLL             |     | FLL     |        | PLL              |           | FLL     |     |

| R1 (kΩ)         | 996 | Rp (kΩ) | 3      | R1 (MΩ)          | 4         | Rp (Ω)  | 503 |

| R2 (kΩ)         | 107 | Cp (pF) | 9      | R2 (k $\Omega$ ) | 107       | Cp (pF) | 53  |

| C(pF)           | 150 | Cs (fF) | 371    | C(pF)            | 150       | Cs (pF) | 2   |

| TABLE II. | JITTER ON RECOVERED CLOCK OF THE CDR WITH VCO |

|-----------|-----------------------------------------------|

|           | OF REF. [5]                                   |

| Parameters                             | with Noisy Power<br>Supply |         |         |

|----------------------------------------|----------------------------|---------|---------|

| Noise amplitude at 10MHz<br>(mV)       | 10                         | 20      | 30      |

| Jitter on Recovered clock<br>ps, (%UI) | 25, (2)                    | 52, (4) | 63, (5) |

| Ripple on Vfine (mV)                   | 50                         | 55      | 60      |

| TABLE III. | BLOCKWISE NOISE PERFORMANCE OF THE CDR WITH |

|------------|---------------------------------------------|

|            | VCO OF REF. [5]                             |

| Parameters                                | With Noisy Power Supply Only<br>On |         |         |        |         |

|-------------------------------------------|------------------------------------|---------|---------|--------|---------|

| Noise of 20mV<br>at 10MHz                 | vco                                | FD      | PD      | СР     | VtoI    |

| Jitter on<br>Recovered clock<br>ps, (%UI) | 50, (4)                            | 11, (1) | 11, (1) | 8, (1) | 16, (1) |

| Ripple on Vfine<br>(mV)                   | 75                                 | 50      | 45      | 50     | 40      |

TABLE IV. JITTER ON RECOVERED CLOCK OF THE CDR WITH PROPOSED VCO

| Parameters                             | with Noisy Power<br>Supply |         | ower    |

|----------------------------------------|----------------------------|---------|---------|

| Noise amplitude (mV) at 10MHz          | 50                         | 100     | 200     |

| Jitter, ps (%UI) on<br>Recovered clock | 23, (2)                    | 34, (3) | 57, (5) |

#### ACKNOWLEDGMENT

The author would like to acknowledge Iraq-India governments for extending facilities and financial support of the Scholarship through Indian Counsel for Cultural Relations (ICCR) and Ministry of Science and Technology of Iraq.

### REFERENCES

- Seema Butala Anand and Behzad Razavi, "A CMOS Clock Recovery Circuit for 2.5-Gb/s NRZ Data", (2001), IEEE Journal of Solid-State Circuits, Vol. 36, No. 3, pp. 432-439.

- [2] Yi-Ju Chen and Monuko du Plessis, "An integrated 0.35 µm CMOS optical receiver with clock and data recovery circuit", (2006), Microelectronics Journal, pp. 985-992.

- [3] Ming-ta Hsieh and Gerald E. Sobelman, "Architectures for Multi-Gigabit Wire-Linked Clock and Data Recovery", (2008), IEEE Circuit & System Magazine, pp. 45-57.

- [4] Bryan Casper and Frank O'Mahony, "Clocking Analysis, Implementation and Measurement Techniques for High-Speed Data Links—A Tutorial", (2009), IEEE Transaction Circuit and System—I: Regular papers, 56(1), pp. 17-39.

- [5] Behzad Razavi, "Phase-Locking in Wire line Systems: Present and Future", (2008), IEEE Custom Integrated Circuits Conference, pp. 615-622.

- [6] Zuoguo (Joe) Wu and Evelina Yeung, "Multi-Gigabit I/O Link Circuit Design Challenges and Techniques", (2007), Electromagnetic Compatibility Symposium.

- [7] Abhijith Arakali, Nema Talebbeydokthi, Srikanth Gondi, and Pavan Kumar Hanumolu, "Supply- Noise Mitigation Techniques in Phase-Locked Loops", (2008), European Solid-State Circuits Conference, pp. 374-377.

- [8] Tzung-Je Lee and Chua-Chin Wang, "A Phase-Locked Loop with 30% Jitter Reduction Using Separate Regulators", (2008), VLSI Design, pp. 1-8.

- [9] Josh Carnes, Igor Vytyaz, Pavan Kumar Hanumolu, and Kartikeya Mayaram, Un-Ku Moon, "Design and analysis of noise tolerant ring oscillators using Maneatis delay cell", (2007), IEEE International Conference on Electronics, Circuits, and Systems, pp. 494-497.

- [10] Marcus van Ierssel, Hisakatsu Yamaguchi, Ali Sheikholeslami, Hirotaka Tamura, and William W. Walker,

"Event-Driven Modeling of CDR Jitter Induced by Power-Supply Noise, Finite Decision-Circuit Bandwidth, and Channel ISI", (2008), IEEE Transaction on Circuits And Systems—I, Vol. 55, No. 5, pp. 1306-1315.

- [11] John G. Maneatis and Mark A. Horowitz, "Precise Delay Generation Using Coupled Oscillators", (1993), IEEE Journal Solid-State and Circuits, VOL. 28, NO. 12, pp. 1273-1282.

- [12] John G. Maneatis, "Low jitter process independent DLL and PLL based on self-biased techniques", (1996), IEEE Journal of Solid-State and Circuits, Vol. 31, No. 11, pp. 1723-1732.

- [13] Keiji Kishine, Kiyoshi Ishii, and Haruhiko Ichino, "Loop-Parameter Optimization of a PLL for a Low-Jitter 2.5-Gb/s One-Chip Optical Receiver IC with 1: 8 DEMUX", (2002), IEEE Journal of Solid-State Circuits, Vol. 37, No. 1, pp. 38-50.

- [14] Xiong Liu, Alan N. Willson, and Jr., "A 3 mW/GHz Near 1-V VCO with Low Supply Sensitivity in 0.18-μm CMOS for SoC Applications", (2009), IEEE International Midwest Symposium on Circuits and Systems pp. 90-93.

- [15] Ming-ta Hsieh, Gerald E. Sobelman, "Architectures for Multi-Gigabit Wire-Linked Clock and Data Recovery", Fourth Quarter (2008), IEEE Circuits and Systems Mag., pp. 45-57.

# A Flexible Sensor-mat to Automate the Process of People Counting

Christof Kutschera\*, Martin Horauer\*, Markus Ray<sup>†</sup>, Daniel Steinmair<sup>‡</sup> and Peter Gorski<sup>§</sup>

\* University of Applied Sciences Technikum Wien, Höchstädtplatz 5,

A-1200 Vienna, Austria, Email: {kutschera, horauer}@technikum-wien.at

<sup>†</sup> Austrian Institute of Technology, Giefinggasse 2, 1210 Vienna, Austria, Email: markus.ray@ait.ac.at

<sup>‡</sup> Bluetechnix GmbH, Lainzerstr. 162/3, A-1130 Vienna, Austria, Email: daniel.steinmair@bluetechnix.at

<sup>§</sup> Getzner Werkstoffe GmbH, Herrenau 5, A-6706 Bürs, Austria, Email: peter.gorski@getzner.com

*Abstract*—Real data on the peoples mobility are an essential input for decision-makers of city and regional planning. They allow for various optimizations like traffic routes, public places or safety measures at public events. Obtaining such data in an automated and reliable way is a burdensome task since usually the requirements on the respective solutions depend on the actual situation (e.g., indoors, outdoors, different counting cross-sections). This paper reports on the work-in-progress of the development for a flexible, low-power sensor-mat that automates people counting.

*Keywords*-sensor-mat; people counter; mobility; wireless networks.

## I. INTRODUCTION

Accurate and representative mobility data, especially for motorized traffic is a vital information for our daily life. It allows for up-to-date traffic control and provides input for spatial planning and resource optimizations of the public infrastructure, see, e.g., [8]). In fact, many automated counting techniques (e.g., [12], [11]) are in use today and have superseded almost all manual counting's. In fact permanent, fully automated counting solutions are installed at many street sections of high interest, delivering reliable traffic data that is used for dynamic speed control information systems, navigation systems, etc.

Respective mobility data for non-motorized traffic, so far, is primarily used by operators of infrastructures like railway stations, airports or shopping malls for various optimizations. For example, using this data one can optimize train schedules and respective transfer times to enhance the attractiveness of public transportation. Likewise, a shopping mall operator can influence the habitual buying behavior and thus better the overall property value. The same data can be used for safety measures in public buildings or at large events by, e.g., restricting access to certain regions when the number of people exceeds the respective capacity. There exist a multitude of automated people counting technologies, see, e.g., [2], [5], or [16]. At present, however, none satisfies all the diverse requirements commonly encountered in practice.

Section II highlights our motivation and lists requirements contributed in a project workshop by various infrastructure operators and urban planners. Next, section III elaborates on related work, before we highlight the challenges and our first concepts in section IV. Finally, we present our status quo before we conclude the paper with an outlook of our next steps.

# II. MOTIVATION AND REQUIREMENTS

Manual people counting's using some sort of tally counter are still frequently performed in practice to gather information on the non-motorized traffic patterns. This manual approach suits short counting's and low to medium traffic densities; especially since almost no installation/setup overhead is required. For longer durations or dense traffic, however, the data gathered using a manual approach is often either not representative or inaccurate. To overcome this issue, many automated people counting approaches exist, see Section III for an overview. However, many of these solutions only fit part of the requirements on an automated people counting system as listed below:

*Costs:* Some solutions for automated people counting necessitate rather high equipment investments (e.g., many solutions based on laser technologies), require elaborate software for data analysis and are costly in terms of extra on-site installations (power and/or network access).

*Flexibility:* Restriction due to local geometries (e.g., at entrance situations) or due to size restrictions of the measurement technology frequently limit the flexibility of existing methods in practice. Furthermore, most automated people counters require dedicated on-site installations.

*Quality:* Especially in dense traffic or extreme environmental situations the automatically gathered data is often inaccurate. Furthermore, for almost all commercial-off-the-shelf people counters no explicit measuring error probability is available, limiting the use of collected data in such situations.

*Environmental Influences:* Several sensors have problems with fluctuations in temperature or lighting – e.g., at entrances – and eventually wind-up delivering incorrect data. Furthermore, only a sub-set of the available solutions can be used out-doors.

*Mobility:* For temporal people counting's spanning several days/weeks (e.g., to optimize pedestrian traffic lights) an autonomous, almost energy self-sufficient system is required. Existing, solutions that fit this requirement are only available

for counting individuals (e.g., using active infra-red sensors).

Data collected via sensor fusion addresses most of the aforementioned requirements, increases, however, the system complexity and costs, cf. [14]. In the project Flexicount we are developing an outdoor capable sensor-mat that enables plug&play counting of people crossing a defined intersection.

# III. RELATED WORK

In recent years different technologies for counting people have been developed and used. The following list gives a short overview and provides an informal assessment of the respective strengths and weaknesses:

Counters based on *active infrared sensors* are typically low-cost, have low power consumption, allow for a simple installation and are portable. These devices, however, are not able to discern between pedestrians and other moving objects (e.g., raindrops) and cannot separate multiple pedestrians crossing a given line-of-sight at the same time.

*Passive infrared counters*, see e.g., [7] and [9], using thermal images are available at moderate costs, feature low energy consumption and are operable in humid or foggy weather conditions. Furthermore, these systems are legally defensible with regard to data privacy. Drawbacks of these devices are their rather limited usability in dense traffic situations, the requirement for over-head installation, the limited co, see [3]verage of widths where counting is feasible and their dependence on temperature differences.

Better counting accuracy is obtained by relying on *laser-scanners*, see [15], [6]. These counters work reasonably well even in crowded areas, allow separation of individuals, usually are simple to setup and can operate on wider cross-sections. Their drawback is mainly due to the high initial costs, their limited usage under different weather conditions and their rather bulky and heavy construction.

*Vision based* counting solutions, see [10], [13], can operate on larger cross-sections, and give somewhat accurate results – some even under varying lighting conditions (stereo vision based systems) and when recorded allow for further postanalysis. These systems are usually simple to setup and require only moderate installations. Drawbacks are influences of the operation on different environmental conditions, legal issues with respect to data privacy, and are often only available for indoor scenarios.

The company eco-counter (http://www.eco-compteur.com) distributes an *acoustic counting solutions* where plates are buried about 5*cm* below the surface. Individuals crossing the respective section get counted by acoustic means. This outdoor capable solution operates in an almost energy self-sufficient way for several years, allows, however, to count only one crossing person per plate. Thus this method is only usable for low traffic density scenarios. Multiple plates are required for bi-directional counting and significant installa-

tion overhead is required. Hence, the solution is best suited for fixed installations.

A solution measuring the change in the *magnetic field* is distributed by the company Future Shape (http://www.future-shape.com) under the product name *SensFloor*. This technology, however, has only limited use for actual people counting's since it was specifically developed for the domain of *ambient assistive living*.

A detailed overview and evaluation of existing people counting solutions was presented in [1] and [4]. Despite all the advances, manual counting's using *tally counters* are still used most of the times, see [3], [4]. For small samples this method is cost-effective and allows high accuracy for low traffic densities. However, bidirectional counting's, higher people traffic densities, and the short time-spans that can be covered in this way limit this method.

# IV. FLEXICOUNT - DEVELOPMENT OF A FLEXIBLE SENSOR-MAT FOR PEOPLE COUNTING

A flexible solution that enables an automated counting of passenger traffic delivering reliable data is needed with growing urbanization and ever increasing traffic. In particular, such a solution should be mobile, allowing to count for several days or weeks, cost effective and require only a minimum of installation and maintenance overhead. In addition it must be adaptable for various different crosssections (counting widths) and robust against environmental influences for outdoor use.

# A. Aims

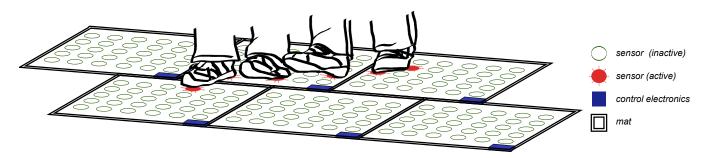

In the project Flexicount we are developing a sensor-mat with integrated sensors that register people traversing the mat. The gathered measurement values are relayed via a wireless sensor network to a host computer that performs the actual analysis and counting. The mats are self-sufficient and can be simply placed beneath each other, hence one can flexibly cover different cross-sections. Figure 1 illustrates the prospective approach.

The following functional requirements will be addressed in Flexicount:

- (r1) sensors to identify people crossing in any direction (ability to discern between people and most other objects)

- (r2) temporal referenced, multi-directional counting's

- (r3) real-time wireless data transmission (plug&play operation)

- (r4) high accuracy with known error probability

- (r5) ability to calibrate the electronics

- (r6) energy self-sufficient operation for multiple weeks

- (r7) polymer-matrix that provides a reasonable load and pressure distribution (e.g., to handle stilettos)

Furthermore, we will address the following non-functional aspects:

Figure 1. Multiple Flexicount mats in operation

- (r8) small weight

- (r9) simple adaption to different cross-section

- (r10) minimum installation and maintenance overhead

- (r11) usable for in- and out-door applications (waterproof, wide temperature range, robustness)

- (r12) safety related features (skid-proof, small mat heights, markings, etc.)

- (r13) hardened against vandalism and denial-of-service

- (r14) low cost

# B. Status Quo

So far, we have developed the sensors with respective control electronics, evaluated some commercial-off-the-shelf wireless radios for our application, and performed a polymer integration with a first prototype.

The sensors – addressing requirements (r1-r2) – basically consist of a multiplexed switch array where contacts are placed at regular intervals (30mm apart) on a 0.15mm thick printed circuit board with a dimension of 450x450mm. On top of this PCB we use a separate contact plane; currently we are evaluating and testing different options with regard to their long-term behaviour (>100.000 load cycles):

- (a) a microwave absorbing elastomer with a volume resistivity of  $4-5\Omega/cm$

- (b) an array of snap-disks with constant force-displacement characteristics

- (c) an elastomer treated with a conductive coating

For the case when we select options (b) or (c) we will complement this sensor array with a number of equidistantly distributed force-sensors. In case option (a) will be selected we are able to omit the latter sensors since the force canöah be directly measured via the contact resistance between the elastomer and the contacts on the printed circuit board. In this case all multiplexed rows must be analog-to-digital converted. First experiments seem promising in this regard, however, a careful long-term evaluation is still under way. Figure 2 shows the mat build-up sequence of an early prototype peeled apart.

For the wireless network we have currently opted for a low-power commercial-off-the-shelf, meshed ZigBee solution; mainly to satisfy the required bandwidth required to

Figure 2. Mat buildup sequence of an early prototype

handle the worst-case data volume, cf. requirement (r3). For an end-product, we will eventually be able to replace ZigBee with ANT — in case we can reduce the transmitted data volume — in order to optimize for low power consumption. Our prototypes' power is currently supplied via a rechargeable battery that is charged occasionally (after some weeks of operation) via an inductive loop (similar to the principle widely employed in electrical tooth-brushes), cf. (r6).

The polymer integration of our prototype is presently build from a 3mm thick viscous elastic polymer at the bottom to accommodate for various different surfaces (e.g., stone chips). Above we use an elastomer to embed the electronic circuitry; this layer must incorporate the various different heights of the devices. On top of this layer we place our contact plate (options (a)-(c) from above) followed by a 3mm thick elastomer that provides the desired load and pressure distribution and serves as protective layer. The top-most layer is made of a sunfast abrasive wear that provides the visible surface finish. The entire polymer embedding is waterproof and enables an outdoor use.

# V. CONCLUSION

This paper presents a work-in-progress report of the development of a sensor-mat that will eventually facilitate an automated counting of peoples traversing the mats. The approach has the potential for use even in dense traffic scenarios both in- and outdoors and will eventually provide a solid data basis for regional planners.

Our next steps are to finalize the long-term evaluations and analysis of our contact planes, before we are able to produce the first prototypes. The latter will than be used for field tests in order to optimize the sensor-mats for the given requirements in a follow-up re-design.

### ACKNOWLEDGMENT

The project FlexiCount has received support by the IV2SPLUS – ways2go program managed by the Austrian Research Agency under grant 825286.

#### REFERENCES

- Bu F., Greene-Roesel R., Diogenes M.C., and Ragland D.R.: Estimating Pedestrian Accident Exposure: Automated Pedestrian Counting Devices Report, Transportation Research Report (TRB 2007), p. 31, March 2007.

- [2] Crabtree M.R.: Smart pedestrian counter system (SPECS), 11<sup>th</sup> International Conference on Road Transport Information and Control, pp. 100–104, 2002.

- [3] Diogenes M., Greene-Roesel R., Arnold L., and Ragland D.: Pedestrian counting methods at intersections: A comparative study, Transportation Research Report (TRB 2007), p. 12, April 2007.

- [4] Greene-Roesel R., Diogenes M., Ragland D., and Lindau L.: Effectiveness of a commercially available automated pedestrian counting device in urban environments: Comparison with manual counts, Proceedings of the 2008 Transportation Research Board 87<sup>th</sup> Annual Meeting: Conference Recordings, pp. 1–17, 2008.

- [5] Gasparini L., Manduchi R., and Gottardi M.: An Ultra-Low-Power Contrast-Based Integrated Camera Node and its Application as a People Counter, Seventh IEEE International Conference on Advanced Video and Signal Based Surveillance (AVSS), pp. 547–554, 2010.

- [6] Huijing Z. and Shibasaki R.: A novel system for tracking pedestrians using multiple single-row laser-range scanners, IEEE Transactions on Systems, Man, and Cybernetics, Vol. 35, Iss. 2, pp. 283–291, 2005.

- [7] Hao Q., et al: *Human tracking with wireless distributed py-roelectric sensors*, IEEE Sensors Journal, Vol. 6, No. 6, pp. 1683–1694, Dec. 2006.

- [8] Haihong F., Jiang P., Shuijin S., and Anke X.: Research on a New Type of City Intelligent Traffic Lights, Control Conference (CCC 2006), pp. 1733–1736, 2006.

- [9] Li N. and Hao Q.: Multiple walker recognition with wireless distributed pyroelectric sensors, Proceedings of SPIE Defense and Security, pp. 694034(1-12), March 2008.

- [10] Rabaud V. and Belongie S.: Counting Crowded Moving Objects, Proceedings of the IEEE Conference on Computer Vision and Pattern Recognition, pp. 705–711, 2006.

- [11] Tanaka M.: Development of traffic counters by laser range scanners, Proceedings of the SICE Annual Conference 2010, pp. 3128–3134, 2010.

- [12] Tseng B.L., Ching-Yung L., and Smith J.R.: *Real-time video surveillance for traffic monitoring using virtual line analysis*, Proceedings of 2002 IEEE International Conference on Multimedia and Expo, 2002 (ICME '02), Vol. 2, pp. 541–544, 2002.

- [13] Teixeira T. and Savvides A.: Lightweight People Counting and Localizing in Indoor Spaces Using Camera Sensor Nodes, ACM/IEEE International Conference on Distributed Smart Cameras, pp. 36–43, 2007.

- [14] Weingand R. and Hehring T.: *Tipps zur Planung eines Personenzählsystems*, Artikel im POS Manager: Fachmagazin für IT-Lösungen und Management im Einzelhandel, Ausgabe 1, pp. 55-57, 2009. (in german)

- [15] Zhao H. and Shibasaki R.: A Real-Time System for Monitoring Pedestrians, 7<sup>th</sup> IEEE Workshop on Application of Computer Vision (WACV/MOTION'05), Vol. 1, pp. 378–385, 2005.

- [16] Zhu Q., Tang L., Jiang Y., and Deng W.: A novel approach of counting people based on stereovision and DSP, The 2nd International Conference on Computer and Automation Engineering (ICCAE), Vol. 1, pp.81–84, 2010.

# Interaction of Semiconductor Laser Chirp with Fiber Dispersion: Impact on WDM Directly Modulated System Performance

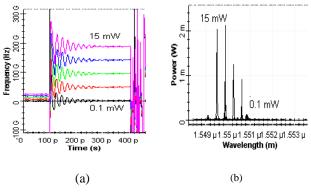

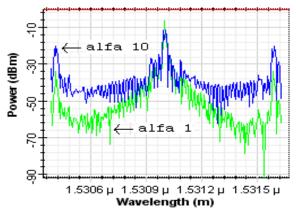

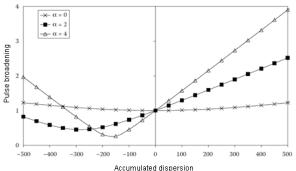

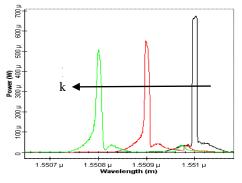

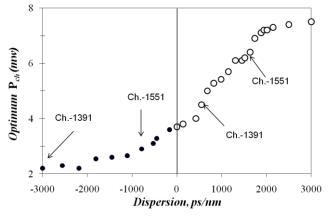

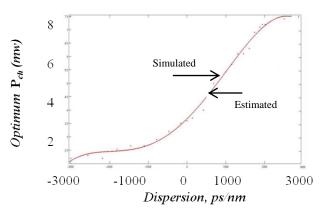

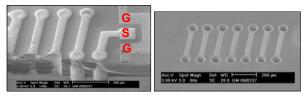

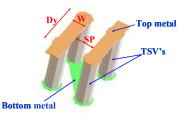

Carmina del Río Campos Dpto. de Sistemas de Información y Telecomunicación Universidad San Pablo CEU Madrid, Spain e-mail: carmina.eps@ceu.es